# PXI Express Software Specification

## PCI EXPRESS eXtensions for Instrumentation

An Implementation of *CompactPCI® Express*

Revision 1.4 March 20, 2020

## **IMPORTANT INFORMATION**

#### Copyright

© Copyright 2005–2020 PXI Systems Alliance. All rights reserved.

This document is copyrighted by the PXI Systems Alliance. Permission is granted to reproduce and distribute this document in its entirety and without modification.

#### NOTICE

The *PXI Express Software Specification* is authored and copyrighted by the PXI Systems Alliance. The intent of the PXI Systems Alliance is for the *PXI Express Software Specification* to be an open industry standard supported by a wide variety of vendors and products. Vendors and users who are interested in developing PXI-compatible products or services, as well as parties who are interested in working with the PXI Systems Alliance to further promote PXI as an open industry standard, are invited to contact the PXI Systems Alliance for further information.

The PXI Systems Alliance wants to receive your comments on this specification. Visit the PXI Systems Alliance web site at http://www.pxisa.org/ for contact information and to learn more about the PXI Systems Alliance.

The attention of adopters is directed to the possibility that compliance with or adoption of the PXI Systems Alliance specifications may require use of an invention covered by patent rights. The PXI Systems Alliance shall not be responsible for identifying patents for which a license may be required by any PXI Systems Alliance specification, or for conducting legal inquiries into the legal validity or scope of those patents that are brought to its attention. PXI Systems Alliance specifications are prospective and advisory only. Prospective users are responsible for protecting themselves against liability for infringement of patents.

The information contained in this document is subject to change without notice. The material in this document details a PXI Systems Alliance specification in accordance with the license and notices set forth on this page. This document does not represent a commitment to implement any portion of this specification in any company's products.

The PXI Systems Alliance makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The PXI Systems Alliance shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Compliance with this specification does not absolve manufacturers of PXI equipment from the requirements of safety and regulatory agencies (UL, CSA, FCC, IEC, etc.).

#### Trademarks

PXI<sup>™</sup> is a trademarks of the PXI Systems Alliance.

PICMG<sup>™</sup> and CompactPCI<sup>®</sup> are trademarks of the PCI Industrial Computation Manufacturers Group.

Product and company names are trademarks or trade names of their respective companies.

## **PXI Express Software Specification Revision History**

This section is an overview of the revision history of the PXI Express Software Specification.

#### Revision 1.0, August 31, 2005

This is the first public revision of the PXI Express Software Specification.

#### Revision 1.1, January 22, 2008

Added 64-bit Windows system framework. Corrected several errata.

#### Revision 1.2, October 18, 2012

Added changes to system description files related to the PXI Trigger Manager described in PXI-9: PXI and PXI Express Trigger Management Specification.

Removed duplication of some sections within and between PXISA Specifications.

Clarified functioning of PXISA System Module, Peripheral Module, and Chassis Drivers.

Peripheral Module Drivers now return an AddressInfo field value that allows other software to locate the device.

Corrected errata.

#### Revision 1.3, May 31, 2018

Added support for the Linux operating system.

Added support for Peripheral Module Drivers to report module slot width and connector alignment, as well as support for Multilink Peripheral Modules.

Added support to the System Module Driver API for efficient batching of SMBus operations.

Clarified versioning requirements in Services Tree.

Updates for new Windows versions.

#### Revision 1.4, March 20, 2020

Addition of ControllerModuleType, SerialNumber, SubModel, and ManufacturerDesc information.

Corrected errata in spelling of PXI1BusSegment section in example Chassis Description File.

Other minor errata.

This Page Intentionally Left Blank

## Contents

#### 1. Introduction

| 1.1 | Objectives                  | . 1 |

|-----|-----------------------------|-----|

|     | Intended Audience and Scope |     |

|     | Background and Terminology  |     |

| 1.4 | Applicable Documents        | . 2 |

#### 2. Hardware Description Files

| 2.1 | Common    | n File Requirements 5                      |  |  |

|-----|-----------|--------------------------------------------|--|--|

|     | 2.1.1     | Version Descriptor                         |  |  |

| 2.2 | System I  | escription Files                           |  |  |

|     | 2.2.1     | System Description Definitions             |  |  |

|     | 2.2.2     | Resource Manager Descriptor                |  |  |

|     | 2.2.3     | System Descriptor                          |  |  |

|     | 2.2.4     | Chassis Descriptor                         |  |  |

|     | 2.2.5     | Trigger Bus Descriptor                     |  |  |

|     | 2.2.6     | Trigger Bridge Descriptor                  |  |  |

|     | 2.2.7     | Line Mapping Specification Descriptor      |  |  |

|     | 2.2.8     | Star System Timing Sets Descriptor         |  |  |

|     | 2.2.9     | Star Trigger Descriptor                    |  |  |

|     | 2.2.10    | Slot Descriptors                           |  |  |

|     |           | 2.2.10.1 System Slot Descriptor            |  |  |

|     |           | 2.2.10.2 Peripheral Slot Descriptor        |  |  |

|     | 2.2.11    | System Description File Example            |  |  |

|     |           | 2.2.11.1 Single-Chassis PXI Express System |  |  |

| 2.3 | Chassis 1 | escription Files                           |  |  |

|     | 2.3.1     | Chassis Description Definitions            |  |  |

|     | 2.3.2     | Chassis Descriptor                         |  |  |

|     | 2.3.3     | Trigger Bus Descriptor                     |  |  |

|     | 2.3.4     | Trigger Bridge Descriptor                  |  |  |

|     | 2.3.5     | Line Mapping Specification Descriptor      |  |  |

|     | 2.3.6     | Star System Timing Sets Descriptor         |  |  |

|     | 2.3.7     | Star Trigger Descriptor                    |  |  |

|     | 2.3.8     | PXI-1 Bus Segment Descriptor               |  |  |

|     | 2.3.9     | Slot Descriptor                            |  |  |

|     | 2.3.10    | Chassis Description File Examples          |  |  |

#### 3. PXI Express Software Services

| 3.1                          | Overview               | N                           | . 35 |

|------------------------------|------------------------|-----------------------------|------|

| 3.2                          | PXI Exp                | ress Components             | 35   |

|                              |                        | Гурез                       |      |

|                              | 3.3.1                  | System Module Drivers       |      |

|                              | 3.3.2                  | Chassis Drivers             | . 41 |

|                              | 3.3.3                  | Peripheral Module Drivers   |      |

|                              | 3.3.4                  | Status Codes                | . 49 |

| 3.4 Registration of Services |                        | tion of Services            | . 49 |

|                              | 3.4.1                  | Services Tree               | 49   |

| 3.5                          | 3.5 System Enumeration |                             | . 51 |

|                              | 3.5.1                  | Resource Manager Algorithm  | 51   |

|                              | 3.5.2                  | Determining Chassis Numbers |      |

|                              | 3.5.3                  | Handling Driver Errors      | 52   |

|                              |                        |                             |      |

#### 4. Software Frameworks and Requirements

| 4.1 | Overvie  | W                                      | . 55 |

|-----|----------|----------------------------------------|------|

| 4.2 | PXI Sof  | tware Compatibility                    | . 55 |

| 4.3 | 32-bit W | /indows System Framework               | . 55 |

|     | 4.3.1    | Introduction                           | . 55 |

|     | 4.3.2    | System Description File Location       | . 55 |

|     | 4.3.3    | System Configuration File Location     | . 55 |

|     | 4.3.4    | Chassis Description File Path Location | . 56 |

|     | 4.3.5    | Driver Software Bindings               | . 56 |

|     | 4.3.6    | Services Tree Implementation           | . 57 |

| 4.4 | 64-Bit V | Vindows System Framework               | . 57 |

|     | 4.4.1    | Introduction                           | . 57 |

|     | 4.4.2    | System Description File Location       | . 57 |

|     | 4.4.3    | System Configuration File Location     | . 57 |

|     | 4.4.4    | Chassis Description File Path Location | . 58 |

|     | 4.4.5    | Driver Software Bindings               | . 58 |

|     | 4.4.6    | Services Tree Implementation           | . 58 |

| 4.5 | 32-bit L | inux System Framework                  | . 59 |

|     | 4.5.1    | Introduction                           | . 59 |

|     | 4.5.2    | System Description File Location       | . 59 |

|     | 4.5.3    | System Configuration File Location     | . 59 |

|     | 4.5.4    | Chassis Description File Path Location | . 59 |

|     | 4.5.5    | Driver Software Bindings               | . 59 |

|     | 4.5.6    | Services Tree Implementation           | . 59 |

|     | 4.5.7    | Security of PXI Files and Interfaces   |      |

| 4.6 | 64-Bit L | inux System Framework                  | . 62 |

|     | 4.6.1    | Introduction                           |      |

|     | 4.6.2    | System Description File Location       | . 62 |

|     | 4.6.3    | System Configuration File Location     |      |

|     | 4.6.4    | Chassis Description File Path Location | . 62 |

|     | 4.6.5    | Driver Software Bindings               |      |

|     | 4.6.6    | Services Tree Implementation           |      |

|     | 4.6.7    | Security of PXI Files and Interfaces   | . 63 |

|     |          |                                        |      |

#### Appendix: 32-Bit Windows System Framework Files

| PXIExpress.h                   | 65 |

|--------------------------------|----|

| PXIExpressSystemModule.def     |    |

| PXIExpressChassis.def          |    |

| PXIExpressPeripheralModule.def |    |

| 1 1                            |    |

#### Appendix: Example Linux Services Tree INI File

| Example Services Tree INI For | Peripheral Module Registration | 71 |

|-------------------------------|--------------------------------|----|

|                               |                                |    |

#### Tables

| Table 2-1. | Version Information Tag Line Descriptions                             | . 5  |

|------------|-----------------------------------------------------------------------|------|

| Table 2-2. | System Description File—System Tag Line Descriptions                  |      |

| Table 2-3. | System Description File—Chassis Tag Line Descriptions                 | . 8  |

| Table 2-4. | System Description File—Trigger Bus Tag Line Descriptions             | . 10 |

| Table 2-5. | System Description File—Star System Timing Sets Tag Line Descriptions | . 11 |

| Table 2-6. | System Description File—Star Trigger Tag Line Descriptions            | . 12 |

| Table 2-7. | System Description File—System Slot Type Enumerated Values            | . 13 |

| Table 2-8. | System Description File—Peripheral Slot Type Enumerated Values        | . 13 |

| Table 2-9.  | System Description File—System Slot Tag Line Descriptions              | 14 |

|-------------|------------------------------------------------------------------------|----|

| Table 2-10. | System Description File—Peripheral Slot Tag Line Descriptions          | 17 |

| Table 2-11. | Chassis Description File-Chassis Tag Line Descriptions                 | 25 |

| Table 2-12. | Chassis Description File-Trigger Bus Tag Line Descriptions             | 27 |

| Table 2-13. | Chassis Description File-Star System Timing Sets Tag Line Descriptions | 28 |

| Table 2-14. | Chassis Description File-Star Trigger Tag Line Descriptions            | 29 |

| Table 2-15. | Chassis Description File-PXI-1 Bus Segment Tag Line Descriptions       | 30 |

| Table 2-16. | Chassis Description File-Slot Tag Line Descriptions                    | 31 |

| Table 3-1.  | Information Field Values                                               | 37 |

| Table 3-2.  | System Module Type Values                                              | 38 |

| Table 3-3.  | Protocol Values                                                        | 39 |

| Table 3-4.  | Information Field Values                                               | 45 |

This Page Intentionally Left Blank

## 1. Introduction

This section explains the objectives and scope of the *PXI Express Software Specification*. It also describes the intended audience and lists relevant terminology and documents. Note that this specification is intended to supplement the *PXI Express Hardware Specification*. Refer to the *PXI Express Hardware Specification* for general background on PXI and its electrical and mechanical requirements.

## 1.1 Objectives

The *PXI Express Software Specification* was created to provide a standard for software support of the new features introduced by the *PXI Express Hardware Specification*. PXI Express brings a rich set of new module types and backplane features. The software specification's purposes are to describe the capabilities of PXI Express hardware components using standard hardware description files and to promote interoperability among PXI Express vendors with respect to software requirements. The software specification addresses a variety of issues, including hardware description, hardware resource management, operating system framework definition, and the incorporation of existing instrumentation software standards.

There are three major objectives for the *PXI Express Software Specification*. The first objective is to define a set of software interfaces for characterizing PXI Express components and their capabilities. The scope of this objective is wider than in previous PXI software specifications. This wider scope is intended to accommodate the powerful new features provided by the *PXI Express Hardware Specification* for PXI Express components, including Chassis self-identification, geographical addressing, and an SMBus. Interfaces in previous PXI Specifications have become more flexible. For example, while PXI-1 controllers had one PCI bus communicating with the PXI backplane, PXI Express controllers will have two or four PCI Express links communicating to the backplane. Each of those links may be routed to the switch fabric with considerable flexibility. In such a flexible system, it becomes necessary for peripheral software components to be responsible for discovering their own device locations, instead of requiring a central resource manager to infer that information from static Chassis description files. As such, the *PXI Express Software Specification* defines requirements for APIs to be implemented by the module vendor and the controller vendor. The specification also defines file formats, component registration mechanisms, and binary linkage to ensure interoperability of these components.

The second objective of this specification is compatibility with previous PXI software specifications. Despite the introduction of a new software architecture, the system description files generated by the resource manager will comply with the *PXI Software Specification*. All software interacting with PXI-1 modules in PXI-1 slots or hybrid slots will continue to function without modification. Additionally, the new module APIs defined in this specification are designed so that they can be implemented independently of the instrument drivers for those modules.

The third objective of this specification is to define standard operating system frameworks and to incorporate existing instrumentation software standards. Additional software requirements include the support of standard operating system frameworks such as Microsoft Windows and Linux, and the support of VISA instrumentation software standards maintained by the IVI Foundation.

## **1.2 Intended Audience and Scope**

This specification is primarily intended for product developers interested in implementing and leveraging software features of the PXI Express platform. Hardware developers will be interested in using these software interfaces for identifying and describing the capabilities of PXI Express hardware products such as Chassis and system controller modules. Likewise, software developers and systems integrators should take advantage of these software interfaces to manage PXI Express resources, including triggers and the local bus, and to implement features such as slot identification and Chassis identification. Additionally, product developers and systems integrators should reference the operating system framework definitions to ensure system-level interoperability. Note that the definitions and requirements described in this document apply to PXI Express

hardware components only (that is, hardware components defined by the PXI-5 specification). The software definitions and requirements for hardware components described by the PXI-1 specification are contained in the PXI-2 specification and are not covered by this document.

### **1.3 Background and Terminology**

This section defines the acronyms and key words referred to throughout this specification. This specification uses the following acronyms:

- API—Application Programming Interface

- CompactPCI—PICMG 2.0 Specification

- PCI—Peripheral Component Interconnect; electrical specification defined by PCISIG

- PCISIG—PCI Special Interest Group

- PICMG—PCI Industrial Computer Manufacturers Group

- **PXI**—PCI eXtensions for Instrumentation

- VISA—Virtual Instrument Software Architecture

- VPP—VXI*plug&play* Specification, maintained by the IVI Foundation.

This specification uses several key words, which are defined as follows:

**RULE:** Rules SHALL be followed to ensure compatibility. A rule is characterized by the use of the words SHALL and SHALL NOT.

**RECOMMENDATION:** Recommendations consist of advice to implementers that will affect the usability of the final module. A recommendation is characterized by the use of the words SHOULD and SHOULD NOT.

**PERMISSION:** Permissions clarify the areas of the specification that are not specifically prohibited. Permissions reassure the reader that a certain approach is acceptable and will cause no problems. A permission is characterized by the use of the word MAY.

**OBSERVATION:** Observations spell out implications of rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules, so that the reader understands why the rule must be followed.

**MAY:** A key word indicating flexibility of choice with no implied preference. This word is usually associated with a permission.

**SHALL:** A key word indicating a mandatory requirement. Designers SHALL implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification. This word is usually associated with a rule.

**SHOULD:** A key word indicating flexibility of choice with a strongly preferred implementation. This word is usually associated with a recommendation.

## **1.4 Applicable Documents**

This specification defines extensions to the base PCI Express and CompactPCI Express specifications referenced in this section. It is assumed that the reader has a thorough understanding of PCI and CompactPCI. The CompactPCI specification refers to several other applicable documents with which the reader may want to become familiar. This specification refers to the following documents directly:

- PXI-1: PXI Hardware Specification

- PXI-2: PXI Software Specification

- PXI-4: PXI Module Description File Specification

- PXI-5: PXI Express Hardware Specification

- PXI-9: PXI and PXI Express Trigger Management Specification

- VPP-4.3: The VISA Library Specification

- PCI Local Bus Specification

- PICMG 2.0 R3.0 CompactPCI Specification

- PICMG EXP.0 R1.0 CompactPCI Express Specification

This Page Intentionally Left Blank

## 2. Hardware Description Files

This section defines the formats of the hardware description files and describes their use.

### 2.1 Common File Requirements

**RULE:** PXI Express Hardware description files SHALL follow the standard text file format for PXI hardware description files defined in *PXI-2: PXI Software Specification*, section 2.2.

#### 2.1.1 Version Descriptor

PXI Express hardware description files include a version descriptor section. The version descriptor allows software to distinguish between . ini file formats as the *PXI Express Software Specification* evolves.

**RECOMMENDATION**: A hardware description file SHOULD include a single version descriptor.

RULE: A version descriptor . ini section SHALL be named "Version".

RULE: Each version descriptor section SHALL contain one of each tag line type described in Table 2-1.

| Tag           | Valid Values                                             | Description                                                                                                                                                                                                                                           |

|---------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Specification | The string "PXI-6".                                      | This field indicates the PXI specification version that the version descriptor applies to.                                                                                                                                                            |

| Major         | <i>x</i> , where <i>x</i> is a positive decimal integer. | This field indicates the major version number<br>of a version <i>x.y</i> , where <i>x</i> is the major number<br>and <i>y</i> is the minor number of the <i>PXI Express</i><br><i>Software Specification</i> version that this file<br>complies with. |

| Minor         | <i>y</i> , where <i>y</i> is a positive decimal integer. | This field indicates the major version number<br>of a version <i>x.y</i> , where <i>x</i> is the major number<br>and <i>y</i> is the minor number of the <i>PXI Express</i><br><i>Software Specification</i> version that this file<br>complies with. |

Table 2-1. Version Information Tag Line Descriptions

#### **Version Descriptor Example**

```

[Version]

Specification = "PXI-6"

Major = 1

Minor = 3

```

**OBSERVATION**: A version descriptor is useful for identifying the *PXI Express Software Specification* file format that a hardware description file complies with. The Specification field can be used to differentiate between hardware description files defined by PXI-2 and PXI-6.

## 2.2 System Description Files

System description files describe PXI Express systems and their components. The system module and one or more PXI Chassis that comprise a PXI Express system determine a system description. A system description enables a variety of software functionality, including geographic slot identification and trigger routing.

Chassis description files, from which much of the system description content is derived, are discussed later in this section.

#### 2.2.1 System Description Definitions

To develop a system description, it is useful to define descriptors for the following PXI Express system components:

- **System**—A PXI Express System descriptor corresponds to a physical PXI Express system. A PXI Express System is a collection of Chassis. Multiple Chassis in a system are coupled in a software-transparent manner (that is, they are coupled via PCI Express switches and other PCI-PCI bridging).

- **Chassis**—A Chassis descriptor corresponds to a physical PXI Chassis in a system. Chassis can include trigger buses, trigger bridges, system timing sets, star triggers, and slots. Line mapping specifications may be used to identify chassis capabilities to the software.

- **Trigger Buses**—A PXI trigger bus descriptor corresponds to a physical trigger bus in a Chassis. A trigger bus is characterized by a list of slots sharing the physical trigger bus connection. Chassis can contain multiple trigger buses.

- **Trigger Bridges**—A PXI trigger bridge descriptor corresponds to a physical trigger bridge in a PXI chassis. Each trigger bridge descriptor represents the possible unidirectional routes that can be established between two buses; if a physical trigger bridge can be used to establish routes in either direction between these buses, two trigger bridge descriptors must represent it, one for each direction. A chassis can contain multiple trigger bridges.

- Line Mapping Specifications—A line mapping specification does not represent a physical chassis component, but sets out the possible routes that a trigger bridge can establish between two adjacent trigger buses. This line mapping provides software with detailed information about the routing capabilities that the chassis supports. These routes can be established through calls made to the chassis Trigger Manager, as described in *PXI-9: PXI and PXI Express Trigger Management Specification*. Multiple line mappings can describe a chassis' routing capabilities.

- Star System Timing Sets—A star system timing set descriptor corresponds to the set of system timing sets contained in a PXI Express Chassis. The system timing sets for a Chassis are characterized by the system timing slot number and a mapping of system timing sets to peripheral slot numbers. A Chassis can contain multiple system timing sets.

- Star Triggers—A PXI star trigger descriptor corresponds to a physical set of star triggers in a Chassis. A set of star triggers is characterized by a star trigger controller slot number and a mapping of PXI\_STAR lines (defined in the *PXI Hardware Specification*) to peripheral slot numbers. A Chassis can contain multiple sets of star triggers.

- **Slots**—A PXI slot descriptor corresponds to a physical slot in a Chassis. A slot is characterized by a geographic address, a PCI logical address, local bus routings, and other special capabilities. A Chassis has multiple slots.

In addition, a *Resource Manager* is defined as the entity responsible for creating a PXI Express system description file. For example, the responsibilities of a Resource Manager might be accomplished by a systems integrator, or a software utility might be provided to automate the Resource Manager algorithm.

**RULE**: A system module manufacturer SHALL provide either a system description file for each supported system configuration or a Resource Manager utility that can manage the system description file.

**RECOMMENDATION**: A system module manufacturer SHOULD provide a utility that can automate the Resource Manager algorithm.

**RULE**: A system description file SHALL be named pxiesys.ini. Refer to the Section 4, *Software Frameworks and Requirements*, to determine the location of the pxiesys.ini file for a given OS platform.

**RECOMMENDATION**: To aid systems integrators and operators, PXI Express module configuration and driver software SHOULD use geographic addressing information, available in a PXI Express system description file, to present chassis and slot locations for PXI Express modules via a user interface.

#### 2.2.2 Resource Manager Descriptor

The resource manager descriptor for the PXI Express System Description File is equivalent to the resource manager descriptor in the PXI System Description File. Refer to *PXI-2: PXI Software Specification* for details of this descriptor.

**RULE**: A Resource Manager SHALL adhere to all rules described in *PXI-2: PXI Software Specification* relating to the system description file resource manager descriptor.

#### 2.2.3 System Descriptor

The system descriptor contains highest-level information about a PXI Express system. PXI Express systems are characterized by the Chassis that comprise the system, and the system descriptor contains a list of these Chassis.

RULE: A system description file SHALL contain one and only one system descriptor.

RULE: The system descriptor .ini section header SHALL be named "System."

RULE: Each system descriptor section SHALL contain one of each tag line types described in Table 2-2.

| Tag         | Valid Values                                                                               | Description                                              |

|-------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------|

| ChassisList | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ . | This tag enumerates the Chassis in a PXI Express system. |

Table 2-2. System Description File—System Tag Line Descriptions

#### System Descriptor Example

```

# This section describes a PXI Express system with two chassis.

[System]

ChassisList = "1,2"

```

**RULE:** A Resource Manager SHALL derive the ChassisList tag value using the algorithm described in Section 3.5.

RULE: Multiple Chassis SHALL be uniquely numbered in the ChassisList tag.

**OBSERVATION:** Chassis can be numbered in an arbitrary fashion. For example, Chassis can be numbered according to their order of discovery using a depth-first PCI traversal algorithm.

#### 2.2.4 Chassis Descriptor

A Chassis descriptor provides a high-level description of an individual PXI Express Chassis in a system. A Chassis descriptor contains collections of the components that comprise a Chassis, including trigger buses, system timing sets, sets of star triggers, and slots.

**RULE:** A system description file SHALL contain a distinct Chassis descriptor for each physical Chassis that comprises the PXI Express system.

**OBSERVATION:** Chassis are enumerated using a system descriptor's ChassisList tag.

**RULE:** A Chassis descriptor SHALL be named "Chassis*N*," where *N* is the Chassis number.

**RULE:** Where a chassis number used in the PXI Express System Description File matches a chassis number used in the PXI System Description File, the number shall refer to the same physical chassis in both System Description Files.

**RULE:** A Resource Manager SHALL derive Chassis numbers from the ChassisList tag of a system descriptor (see Table 2-2).

**RECOMMENDATION:** The Chassis number SHOULD be physically viewable on a Chassis to assist operators in locating Peripheral Modules.

RULE: Each Chassis descriptor SHALL contain one of each of tag line type described in Table 2-3.

| Tag                 | Valid Values                                                                                                                                                    | Description                                                                                                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Model               | A string indicating the model name for this Chassis.                                                                                                            | This tag identifies a Chassis model name.                                                                  |

| Vendor              | A string indicating the vendor name for this Chassis.                                                                                                           | This tag identifies a Chassis vendor name.                                                                 |

| SerialNumber        | A 13-byte string specifying the backplane serial number.                                                                                                        | Refer to the CompactPCI Express<br>specification for details regarding the<br>format of the serial number. |

| SlotList            | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ .                                                                      | This tag enumerates the slots in a Chassis.                                                                |

| TriggerBusList      | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ .                                                                      | This tag enumerates the trigger buses in a Chassis.                                                        |

| TriggerBridgeList   | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ .                                                                      | This tag enumerates the trigger bridges in a chassis.                                                      |

| LineMappingSpecList | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ .                                                                      | This tag enumerates the line mapping specifications that exist for a chassis.                              |

| TriggerManager      | A string indicating the path in<br>the <i>Trigger Managers</i> portion of<br>the services tree that indicates<br>the trigger manager to use for<br>the chassis. | This tag identifies where to locate trigger<br>manager information for the chassis.                        |

| Table 2-2  | System Description File_Chassis Tag Line Descr  | intione |

|------------|-------------------------------------------------|---------|

| Table 2-9. | System Description File—Chassis Tag Line Descri | iptions |

| StarSystemTimingSetList | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ . | This tag enumerates the PXI Express<br>system timing sets in a Chassis.                                                                                                       |

|-------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DescriptionFile         | A string indicating the filename<br>of the chassis description file for<br>the chassis.    | This tag identifies the filename of the chassis description file. Refer to section 2.3, <i>Chassis Description Files</i> , for information about the location of these files. |

| StarTriggerList         | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ . | This tag enumerates the sets of star triggers in a Chassis.                                                                                                                   |

#### **Chassis Descriptor Example**

```

# This example describes an 18-slot PXI Express chassis with 12

# peripheral slots (slots 2-13), four hybrid slots (slots 14-17), and

# one PXI-1 slot (slot 18). The chassis has three trigger buses with

# two bidirectional trigger bridges that have equivalent routing

# capabilities.

[Chassis1]

Model = "ABC1234"

Vendor = "Acme"

DescriptionFile = "Acme ABC1234.ini"

SerialNumber = "000038a2e941"

SlotList = "1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18"

TriggerBusList = "1,2,3"

TriggerBridgeList = "1,2,3,4"

LineMappingSpecList = "1"

TriggerManager = "Acme\ABC1234"

StarSystemTimingSetList = "1"

StarTriggerList = "1"

```

**RULE:** A Resource Manager SHALL derive the nonshaded tag values in Table 2-3 from the tag values of the corresponding Chassis description file's Chassis descriptor (see Table 2-11).

**RULE:** A Resource Manager SHALL set the TriggerBridgeList and LineMappingSpecList tag values to an empty list if the corresponding Chassis description file's Chassis descriptor does not contain these tags.

**RULE:** A Resource Manager SHALL derive the SerialNumber tag value using the Chassis EPROM, accessed via the System Module Driver interface described in Section 3.3.1, *System Module Drivers*.

**RULE:** A Resource Manager SHALL determine the TriggerManager tag value for the chassis using the same mechanism described in *PXI-2: PXI Software Specification*.

**OBSERVATION:** The StarSystemTimingSetList tag in the chassis descriptor enumerates the list of Star System Timing Sets descriptors that exist for a particular chassis. It should be considered independent of sets of PXIe\_DSTAR*Xn* lines, which are enumerated within the Star System Timing Sets descriptors. The reuse of this name for both purposes is maintained for backward compatibility.

#### 2.2.5 Trigger Bus Descriptor

A trigger bus descriptor describes an individual trigger bus in a PXI Express Chassis. A trigger bus is characterized by a list of slots that reside on the trigger bus.

**RULE:** A system description file SHALL contain a distinct PXI Express trigger bus descriptor for each physical PXI trigger bus in the system.

**RULE:** A trigger bus descriptor SHALL be named "Chassis*M*TriggerBus*N*," where *M* is the Chassis number and *N* is the trigger bus number.

**RULE:** A Resource Manager SHALL derive trigger bus numbers from the TriggerBusList tag of the corresponding Chassis descriptor (see Table 2-3).

**OBSERVATION:** While each trigger bus number will uniquely correspond to a set of PXI Express slots, there is not necessarily a one-to-one correspondence between trigger buses and PCI bus segments.

RULE: Each trigger bus descriptor SHALL contain one of each of the tag line types described in Table 2-4.

| Tag      | Valid Values                                                                               | Description                                     |

|----------|--------------------------------------------------------------------------------------------|-------------------------------------------------|

| SlotList | A comma-separated list of $n$ ,<br>where $n$ is a decimal integer<br>such that $n \ge 1$ . | This tag enumerates the slots on a trigger bus. |

Table 2-4.

System Description File—Trigger Bus Tag Line Descriptions

#### **Trigger Bus Descriptor Example**

```

# This example describes an 8-slot PXI Express chassis with two

# peripheral slots (slots 2-3), four hybrid slots (slots 4-7), and

# one PXI-1 slot (slots 8).

# The trigger bus spans all eight slots.

[Chassis1TriggerBus1]

SlotList = "1,2,3,4,5,6,7,8"

```

**RULE:** A Resource Manager SHALL derive the tag values in Table 2-4 from the tag values of the corresponding Chassis description file's Trigger Bus descriptor (see Table 2-12).

#### 2.2.6 Trigger Bridge Descriptor

The Trigger Bridge Descriptor for the PXI Express System Description File is equivalent to the Trigger Bridge Descriptor in the PXI System Description File. Refer to *PXI-2: PXI Software Specification* for details of this descriptor.

**RULE:** A Resource Manager SHALL adhere to all rules described in *PXI-2: PXI Software Specification* relating to the system description file trigger bridge descriptor.

#### 2.2.7 Line Mapping Specification Descriptor

The Line Mapping Specification Descriptor for the PXI Express System Description File is equivalent to the Line Mapping Specification Descriptor in the PXI System Description File. Refer to *PXI-2: PXI Software Specification* for details of this descriptor.

**RULE:** A Resource Manager SHALL adhere to all rules described in *PXI-2: PXI Software Specification* relating to the system description file line mapping specification descriptor.

#### 2.2.8 Star System Timing Sets Descriptor

A star system timing sets descriptor describes the system timing sets in a PXI Express Chassis. A star system timing sets descriptor is characterized by a system timing slot number and a mapping of system timing sets (that is, PXIe\_DSTARAn, PXIe\_DSTARBn, and PXIe\_DSTARCn) to peripheral slot numbers.

**RULE:** A system description file SHALL contain a distinct star system timing sets descriptor for each system timing slot in the system.

**RULE:** A star system timing sets descriptor SHALL be named "*ChassisMStarSystemTimingSetsN*," where *M* is the Chassis number and *N* is the number for the system timing sets.

**RULE:** A Resource Manager SHALL derive star system timing sets descriptor numbers from the StarSystemTimingSetsList tag of the corresponding Chassis descriptor (see Table 2-3).

**OBSERVATION:** The StarSystemTimingSetList tag in the chassis descriptor enumerates the list of Star System Timing Sets descriptors that exist for a particular chassis. It should be considered independent of sets of PXIe\_DSTAR*Xn* lines, which are enumerated within the Star System Timing Sets descriptors. The reuse of this name for both purposes is maintained for backward compatibility.

**RULE:** A star system timing sets descriptor SHALL contain one of each of the tag line types described in Table 2-5.

| Tag                                                                                                                                                                   | Valid Values                                                                                                                          | Description                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| SystemTimingSlot                                                                                                                                                      | A decimal integer <i>n</i> , where <i>n</i> is a decimal integer such that $n \ge 1$ .                                                | This tag specifies the slot number of the system timing slot for this group of system timing sets.                                |

| StarSystemTimingSet <i>n</i> (where <i>n</i> is a decimal integer such that $0 \le n \le 16$ ), for each possible system timing set for a given system timing module. | A decimal integer <i>m</i> , where <i>m</i> is<br>the number of the PXI slot that<br>connects to Star System Timing<br>Set <i>n</i> . | This tag specifies the peripheral slot<br>number corresponding to a set of<br>PXIe_DSTARA, PXIe_DSTARB, and<br>PXIe_DSTARC lines. |

Table 2-5. System Description File—Star System Timing Sets Tag Line Descriptions

#### Star System Timing Sets Descriptor Example

```

# This example describes an 8-slot PXI Express chassis with two

# peripheral module slots (2-3), four hybrid slots (4-7), and one

# PXI-1 slot (8).

# The system timing set controller slot is slot 4, and the system

# timing set mapping to each hybrid peripheral slot is described.

[Chassis1StarSystemTimingSets1]

SystemTimingSlot = 4

StarSystemTimingSet0 = 4

StarSystemTimingSet1 = 2

StarSystemTimingSet2 = 3

StarSystemTimingSet3 = 5

StarSystemTimingSet4 = 6

StarSystemTimingSet5 = 7

```

**RULE:** A Resource Manager SHALL derive the tag values in Table 2-5 from the tag values of the corresponding Chassis description file's star system timing sets descriptor (see Table 2-14).

**OBSERVATION:** The star system timing sets descriptor allows configuration software to describe alternative system timing sets to slot mappings.

**OBSERVATION:** If a star system timing set is not routed to a PXI Express slot, the corresponding StarSystemTimingSet*n* tag will not be listed in the star system timing sets descriptor.

#### 2.2.9 Star Trigger Descriptor

A star trigger descriptor describes an individual set of star triggers in a PXI Express Chassis. A star trigger descriptor is characterized by a star trigger controller slot number and a mapping of PXI\_STAR lines, as defined in the *PXI Express Hardware Specification*, to peripheral slot numbers.

**RULE:** A system description file SHALL contain a distinct PXI star trigger descriptor for each physical set of PXI star triggers in the system.

**RULE:** A star trigger descriptor SHALL be named "Chassis*M*StarTrigger*N*," where *M* is the Chassis number and *N* is the number for the set of star triggers.

**RULE:** A Resource Manager SHALL derive star trigger descriptor numbers from the StarTriggerList tag of the corresponding Chassis descriptor (see Table 2-3).

RULE: Each star trigger descriptor SHALL contain one of each of the tag line types described in Table 2-6.

| Tag                                                                                                                                                   | Valid Values                                                                                                                                  | Description                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| SystemTimingSlot                                                                                                                                      | <i>n</i> , where <i>n</i> is a decimal integer such that $n \ge 1$ .                                                                          | This tag specifies the star trigger controller slot number for a PXI_STAR lines in a set of star triggers. |

| PXI_STAR <i>n</i> (where <i>n</i> is a decimal integer such that $0 \le n$ $\le 16$ ), for each PXI star trigger line physically routed to a PXI slot | A decimal integer <i>m</i> , where <i>m</i> is<br>the number of the PXI slot that<br>connects to the star trigger line<br>PXI_STAR <i>n</i> . | This tag specifies the PXI_STAR line to slot mapping for a set of star triggers.                           |

Table 2-6.

System Description File—Star Trigger Tag Line Descriptions

#### **Star Trigger Descriptor Example**

```

# This example describes an 8-slot PXI Express chassis with two

# peripheral slots (slots 2-3), four hybrid slots (slots 4-7), and

# one PXI-1 slot (slots 8).

# The star trigger controller slot is slot 4.

[Chassis1StarTrigger1]

SystemTimingSlot = 4

PXI_STAR0 = 1

PXI_STAR1 = 2

PXI_STAR2 = 3

PXI_STAR3 = 5

PXI_STAR4 = 6

PXI_STAR5 = 7

PXI_STAR6 = 8

```

**RULE:** A Resource Manager SHALL derive the tag values in Table 2-6 from the tag values of the corresponding Chassis description file's Star Trigger descriptor (see Table 2-14).

12

**OBSERVATION:** The star trigger descriptor allows configuration software to describe alternative star trigger line mappings.

**OBSERVATION:** If a star trigger line is not routed to a PXI Express slot, the corresponding PXI\_STAR*n* tag will not be listed in the star trigger bus descriptor.

#### 2.2.10 Slot Descriptors

Slot descriptors describe slots in PXI Express Chassis. PXI Express defines several slot types, including the system slot, and several types of peripheral slots.

A PXI Express Chassis' identification EPROM describes the type of slot implemented for a given slot number. The System Description Files includes this slot type information to enable simplified access for application software. Refer to the PXI Express Hardware Specification for detailed information about the types of possible slots in a PXI Express Chassis.

The following System Slot type values are defined:

| Valid Values          | Description                                                                  |  |

|-----------------------|------------------------------------------------------------------------------|--|

| "PXIeSystemSlot2Link" | This tag value indicates that the system slot routes two PCI Express links.  |  |

| "PXIeSystemSlot4Link" | This tag value indicates that the system slot routes four PCI Express links. |  |

#### Table 2-7. System Description File—System Slot Type Enumerated Values

The following Peripheral Slot type values are defined:

| Valid Values           | Description                                                                               |

|------------------------|-------------------------------------------------------------------------------------------|

| "PXIePeripheralSlot"   | The tag value indicates that the peripheral slot is a PXI<br>Express peripheral slot.     |

| "PXIeHybridSlot"       | This tag value indicates that the peripheral slot is a PXI Express Hybrid slot.           |

| "PXIeSystemTimingSlot" | This tag value indicates that the peripheral slot is a PXI<br>Express System Timing slot. |

| "PXI-1Slot"            | This tag value indicates that the peripheral slot is a PXI-1 slot.                        |

| Table 2-8. | System D | Description | File—F | Peripheral | Slot Type | Enumerated | Values |

|------------|----------|-------------|--------|------------|-----------|------------|--------|

#### 2.2.10.1 System Slot Descriptor

A system slot descriptor describes the system slot in a PXI Express Chassis. A system slot descriptor is characterized by the features of the slot it describes, including manufacturer and model information for a module present in the slot, the type of Chassis slot, and PCI Express link widths for the backplane slot and peripheral module.

**RULE:** A system description file SHALL contain a single system slot descriptor for each physical system slot in the PXI Express system.

**RULE:** A system slot descriptor SHALL be named "Chassis*M*Slot*N*," where *M* is the Chassis number, and *N* is the physical slot number.

**OBSERVATION:** A PXI Express system slot will always be numbered 1 for a given Chassis. Refer to the *PXI Express Hardware Specification* for more information.

RULE: Each system slot descriptor SHALL contain one of each of tag line types described in Table 2-9.

| Tag                  | Valid Values                                                                                                                                                       | Description                                                                                                                                                                                                         |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model                | A string value.                                                                                                                                                    | This tag identifies the model name for<br>the PXI Express system module<br>residing in the slot.                                                                                                                    |

| Vendor               | A string value.                                                                                                                                                    | This tag identifies the vendor name<br>for the PXI Express system module<br>residing in the slot.                                                                                                                   |

| InstanceName         | A string value that matches the name<br>string returned by the corresponding<br>System Module Driver's<br><i>PXISA_SystemModule_GetName</i><br>function.           | This tag specifies a unique name for<br>the System Module instance.                                                                                                                                                 |

| AddressInfo          | A string value that matches<br>the addressInfo string<br>returned by the corresponding<br>System Module Driver's<br><i>PXISA_SystemModule_GetName</i><br>function. | This tag specifies additional<br>addressing info for the System<br>Module instance. Refer to<br>section 3.3.1, <i>System Module Drivers</i> ,<br>for more information about the value<br>of the AddressInfo string. |

| SlotType             | A string value corresponding to the<br>enumerated values specified in<br>Table 2-7.                                                                                | This tag specifies the type of system slot.                                                                                                                                                                         |

| SystemSlotLinkWidth1 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 1, 4$ , or 8.                                                                                        | This tag specifies the routed link<br>width of the PCI Express Link<br>Number 1 of the system slot.                                                                                                                 |

| SystemSlotLinkWidth2 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 1, 4, 8$ , or 16.                                                                                    | This tag specifies the routed link<br>width of the PCI Express Link<br>Number 2 of the system slot.                                                                                                                 |

| SystemSlotLinkWidth3 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4$ .                                                                                           | This tag specifies the routed link<br>width of the PCI Express Link<br>Number 3 of the system slot.                                                                                                                 |

**Table 2-9.** System Description File—System Slot Tag Line Descriptions

| SystemSlotLinkWidth4       | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4$ .        | This tag specifies the routed link<br>width of the PCI Express Link<br>Number 4 of the system slot.    |

|----------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| LocalBusRight              | A valid slot descriptor.<br>(Other).                                            | This tag indicates how a slot routes its<br>Local Bus pin(s) to the right.                             |

| ControllerModuleLinkWidth1 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 1, 4$ , or 8.     | This tag specifies the maximum link<br>width of the PCI Express Link<br>Number 1 of the system module. |

| ControllerModuleLinkWidth2 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 1, 4, 8$ , or 16. | This tag specifies the maximum link<br>width of the PCI Express Link<br>Number 2 of the system module. |

| ControllerModuleLinkWidth3 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4$ .        | This tag specifies the maximum link<br>width of the PCI Express Link<br>Number 3 of the system module. |

| ControllerModuleLinkWidth4 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4$ .        | This tag specifies the maximum link<br>width of the PCI Express Link<br>Number 4 of the system module. |

| ControllerModuleType       | A string value, <i>Embedded</i> or <i>Remote</i> .                              | This tag describes the type of the system module.                                                      |

| SerialNumber               | A non-empty string.                                                             | This tag describes the serial number<br>for the system module.                                         |

| SubModel                   | A non-empty string.                                                             | This tag describes the submodel for<br>the system module.                                              |

#### System Slot Descriptor Example

```

# This example describes an 8-slot PXI Express chassis with two

# peripheral slots (slots 2-3), four hybrid slots (slots 4-7), and

# one PXI-1 slot (slots 8).

[Chassis1Slot1]

Model = "Example PXI Express System Model"

Vendor = "Example PXI Express System Vendor"

InstanceName = "Example PXI Express System Module, Instance Number 1"

AddressInfo = "SYSTEMMODULE::1"

SlotType = "PXIeSystemSlot2Link"

SystemSlotLinkWidth1 = 8

```

```

SystemSlotLinkWidth2 = 16

SystemSlotLinkWidth3 = 0

SystemSlotLinkWidth4 = 0

LocalBusRight = "Chassis1Slot2"

ControllerModuleLinkWidth1 = 1

ControllerModuleLinkWidth2 = 1

ControllerModuleLinkWidth3 = 0

ControllerModuleLinkWidth4 = 0

ControllerModuleType = "Embedded"

SubModel = "QCG3RHD1"

SerialNumber = "B8274CE2"

```

**RULE:** A Resource Manager SHALL derive the Model, Vendor, InstanceName, AddressInfo, ControllerType, SubModel, SerialNumber, and ControllerModuleLinkWidth*n* tag values using the System Module Driver interfaces defined in Section 3.3.1.

**RULE:** If the ControllerModuleType, Serial Number, or Submodel of a System Module is not available from its System Module Driver, a Resource Manager SHALL omit the unavailable tag(s) from the System Slot Descriptor.

**RULE:** A Resource Manager SHALL derive the SlotType and SystemSlotLinkWidth*n* tag values from the corresponding values in the PXI Express Chassis' configuration EPROM. Refer to the CompactPCI Express specification for complete discussion of a Chassis' backplane capability record.

**OBSERVATION:** A PXI Express chassis' EPROM is accessed using the System Module Driver Interface defined in Section 3.3.1, *System Module Drivers*.

**RULE:** A Resource Manager SHALL derive the LocalBusRight tag values from the corresponding values in the PXI Express Chassis Description File.

**OBSERVATION:** Software can use the value of the AddressInfo tag to locate PCI and PCI Express devices on a system module, assuming such devices are exposed by the System Module Driver.

#### 2.2.10.2 Peripheral Slot Descriptor

A peripheral slot descriptor describes an individual peripheral slot in a PXI Express Chassis, and the PXI Express peripheral module that occupies the slot, if one exists. A peripheral slot descriptor is characterized by the features of the slot it describes, including routing information for the slot's local bus lines and the PCI logical address for the module.

**RULE:** A system description file SHALL contain a distinct peripheral slot descriptor for each physical peripheral slot in the PXI Express system.

**RULE:** A slot descriptor SHALL be named "Chassis*M*Slot*N*," where *M* is the Chassis number, and *N* is the physical slot number.

**RULE:** A Resource Manager SHALL derive peripheral slot numbers from the SlotList tag of the corresponding Chassis descriptor (see Table 2-3).

RULE: Each slot descriptor SHALL contain one of each of nonshaded tag line type described in Table 2-10.

| Тад                      | Valid Values                                                                                                                                                              | Description                                                                                                                                                                                                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model                    | A string value.                                                                                                                                                           | This tag identifies the<br>model name for the PXI<br>Express peripheral module<br>residing in the slot.                                                                                                                                  |

| Vendor                   | A string value.                                                                                                                                                           | This tag identifies the<br>vendor name for the PXI<br>Express peripheral module<br>residing in the slot.                                                                                                                                 |

| InstanceName             | A string value that matches the name<br>string returned by the corresponding<br>Peripheral Module Driver's<br><i>PXISA_PeripheralModule_GetName</i><br>function.          | This tag specifies a unique<br>name for the Peripheral<br>Module instance.                                                                                                                                                               |

| AddressInfo              | A string value that matches<br>the addressInfo string returned<br>by the corresponding<br>Peripheral Module Driver's<br><i>PXISA_PeripheralModule_GetName</i><br>function | This tag specifies<br>additional addressing info<br>for the Peripheral Module<br>instance. Refer to<br>section 3.3.3, <i>Peripheral</i><br><i>Module Drivers</i> , for more<br>information about the value<br>of the AddressInfo string. |

| SlotType                 | A string value corresponding to the<br>enumerated values specified in<br>Table 2-8.                                                                                       | This tag specifies the type of PXI Express slot.                                                                                                                                                                                         |

| SystemSlotLinkOrigin1    | <i>n</i> , where <i>n</i> is a decimal integer such that $0 \le n \le 4$ .                                                                                                | This tag specifies which<br>System Slot Link Number<br>this slot's Links are directly<br>or indirectly (via Switch or<br>Bridge) connected to.                                                                                           |

| SystemSlotLinkOrigin2    | <i>n</i> , where <i>n</i> is a decimal integer such that $0 \le n \le 4$ .                                                                                                | This tag specifies which<br>System Slot Link the<br>Bridge originates from for<br>Hybrid Slots and PXI-1<br>Slots.                                                                                                                       |

| PeripheralSlotLinkWidth1 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4, \text{ or } 8.$                                                                                    | This tag specifies the<br>routed link width of this<br>slot's PCI Express Link<br>Number 1.                                                                                                                                              |

| PeripheralSlotLinkWidth2 | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4, 8$ , or 16.                                                                                        | This tag specifies the<br>routed link width of this<br>slot's PCI Express Link<br>Number 2.                                                                                                                                              |

| Table 2-10  | System Description File |                     | I in A Descriptions |

|-------------|-------------------------|---------------------|---------------------|

| Table 2-10. | System Description rile | —renpheral Slut rat |                     |

| LocalBusLeft                        | A valid slot descriptor.<br>A valid star trigger descriptor.<br>(Other).              | This tag indicates how a slot routes its Local Bus pin(s) to the left.                                 |

|-------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| LocalBusRight                       | A valid slot descriptor.<br>(Other).                                                  | This tag indicates how a slot routes its Local Bus pin(s) to the right.                                |

| PeripheralModuleLinkWidthMax        | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4, 8$ , or 16.    | This tag specifies the<br>maximum link width<br>supported by the peripheral<br>module in this slot.    |

| PeripheralModuleLinkWidthNegotiated | <i>n</i> , where <i>n</i> is a decimal integer such that $n = 0, 1, 4, 8$ , or 16.    | This tag specifies the actual<br>negotiated link width for<br>the peripheral module in<br>this slot.   |

| PeripheralModuleOccupiedSlotList    | A comma-separated list of decimal integers, where each is greater than or equal to 2. | This tag specifies the list of<br>physical slots consumed by<br>the peripheral module in<br>this slot. |

| SerialNumber                        | A non-empty string.                                                                   | This tag specifies the serial<br>number for the peripheral<br>module.                                  |

| SubModel                            | A non-empty string.                                                                   | This tag specifies the submodel for the peripheral module.                                             |

| ManufacturerDesc                    | A non-empty string.                                                                   | This tag specifies the<br>manufacturer description<br>for the peripheral module.                       |

#### **Peripheral Slot Descriptor Example**

```

# This example describes Slot 4 of an 8-slot PXI Express chassis.

# The slot is a peripheral slot that connects to a PCI

# Express switch that originates from the system slot's Link #1.

# The link width is x4, and a x1 PXI Express module is present.

[Chassis1Slot4]

Model = "Example PXI Express Model"

Vendor = "Example PXI Express Vendor"

InstanceName = "Example PXI Express Peripheral Module, Instance #1"

AddressInfo = "PXI0::2-19.0::INSTR;PXICARD2::19::0"

SlotType = "PXIePeripheralSlot"

SystemSlotLinkOrigin1 = 1

SystemSlotLinkOrigin2 = 0

PeripheralSlotLinkWidth1 = 4

PeripheralSlotLinkWidth2 = 0

LocalBusLeft = "Chassis1Slot3"

LocalBusRight = "Chassis1Slot5"

PeripheralModuleLinkWidthMax = 1

```

PeripheralModuleLinkWidthNegotiated = 1

PeripheralModuleOccupiedSlotList = "4"

SerialNumber = "ADF33E20"

SubModel = "16CH"

ManufacturerDesc = "Data Acquisition Device"

**RULE:** A Resource Manager SHALL derive the Model, Vendor, InstanceName, AddressInfo tag, SerialNumber, SubModel, and ManufacturerDesc values using the Peripheral Module Driver interfaces described in Section 3.3.3.

**RULE:** If the Serial Number, Submodel, or Manufacturer Description of a Peripheral Module is not available from its Peripheral Module Driver, a Resource Manager SHALL omit the unavailable tag(s) from the Peripheral Slot Descriptor.

**RULE:** A Resource Manager SHALL derive the SlotType, SystemSlotLinkOrigin*n*, and PeripheralSlotLinkWidth*n* tag values from the corresponding values in the PXI Express Chassis' configuration EPROM. Refer to the CompactPCI Express specification for complete discussion of a Chassis' backplane capability record.

**OBSERVATION:** A PXI Express chassis' EPROM is accessed using the System Module Driver Interface defined in Section 3.3.1, *System Module Drivers*.

**RULE:** A Resource Manager SHALL derive the LocalBusLeft and LocalBusRight tag values from the corresponding values in the PXI Express Chassis Description File.

**OBSERVATION:** Software can use the value of the AddressInfo tag to locate PCI and PCI Express devices on the peripheral module.

**RULE:** A PXI Express Resource Manager SHALL derive the PeripheralModuleLinkWidthMax, PeripheralModuleLinkWidthNegotiated, and PeripheralModuleOccupiedSlotList tag values using the Peripheral Module Driver Interface defined in Section 3.3.3, *Peripheral Module Drivers*.

**RULE:** For each Peripheral Module reported by a Peripheral Module Driver, a PXI Express Resource Manager SHALL populate the shaded tag line types in Table 2-10 in exactly one slot, where that slot matches the Slot Number field reported by the Peripheral Module Driver for that Peripheral Module.

**OBSERVATION:** Section 3.3.3, *Peripheral Module Drivers*, describes how a Multilink Peripheral Module may connect to the chassis backplane through two or more PCI Express links, in which case the Peripheral Module Driver(s) will report a separate Peripheral Module for each of these links. In accordance with the above RULE, a Resource Manager will record that information in multiple Peripheral Slot Descriptors in the System Description File. A client, such as a vendor-supplied user interface, can determine that multiple Peripheral Slot Descriptors refer to the same Multilink Peripheral Module because they have the same tag values for the Vendor, Model, and PeripheralModuleOccupiedSlotList tag lines.

**OBSERVATION:** While a peripheral module may physically consume multiple slots, it should be reported only once in the System Description File for each PCI Express link that connects it to the backplane. This preserves backward compatibility for clients that do not comprehend multislot modules, while the PeripheralModuleOccupiedSlotList tag line provides the necessary information to clients that consume it.

**RULE:** For Peripheral Modules whose Peripheral Module Drivers do not report the Occupied Slot Count and Slot Number Offset fields, a PXI Resource Manager SHALL populate the PeripheralModuleOccupiedSlotList tag line with a value of *SlotNumber*, where *SlotNumber* is the Slot Number reported by the Peripheral Module Driver.

#### 2.2.11 System Description File Example

This section provides a complete example of a PXI Express System Description file.

#### 2.2.11.1 Single-Chassis PXI Express System

The following example system includes a single PXI Express Chassis. The Chassis described includes peripheral slots, hybrid slots, and a single PXI-1 slot. In addition, the Chassis includes modules in each slot.

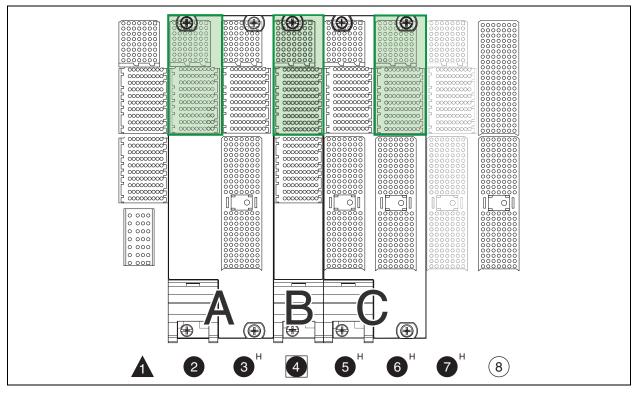

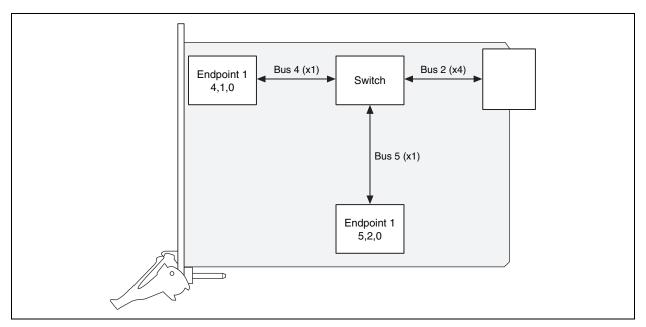

The PXI Express Chassis includes a 4-link system controller slot (slot 1), two hybrid slots (slots 2-3), a system timing slot (slot 4), and four PXI-1 slots (slots 5-8). The backplane is a 4-link configuration, routing link 1 to slot 2, link 2 to slot 3, link 3 to slot 4, and link 4 to a PCIe-to-PCI bridge that forms that bus for the hybrid and legacy slots.

Refer to the following figure for a graphical representation of the PXI Express backplane in this system, with modules overlaid in some slots. The highlighted areas over the PXI Express connectors indicate on which slots the modules connect to the backplane.

Figure 2-1. PXI Express Backplane

```

# This section describes a PXI Express system with one 8-slot chassis.

[System]

ChassisList = 1

[Chassis1]

Model = "Example 8-Slot Chassis"

Vendor = "Example Chassis Vendor"

DescriptionFile = "Example Chassis Vendor Example 8-Slot Chassis.ini"

SerialNumber = "000038a2e941"

SlotList = "1,2,3,4,5,6,7,8"

```

```

TriggerBusList = "1,2"

TriggerBridgeList = "1,2"

LineMappingSpecList = "1"

StarSystemTimingSetList = "1"

StarTriggerList = "1"

# Each trigger bus spans a subset of the eight slots.

[Chassis1TriggerBus1]

SlotList = "1,2,3,4"

[Chassis1TriggerBus2]

SlotList = "5,6,7,8"

# There is a bidirectional trigger bridge between trigger

# bus 1 and trigger bus 2

[Chassis1TriggerBridge1]

SourceTriggerBus = 1

DestinationTriggerBus = 2

LineMappingSpec = 1

[Chassis1TriggerBridge2]

SourceTriggerBus = 2

DestinationTriggerBus = 1

LineMappingSpec = 1

# The trigger bridge supports a straight-through mapping

[Chassis1LineMappingSpec1]

PXI_TRIG0 = "0"

PXI_TRIG1 = "1"

PXI_TRIG2 = "2"

PXI_TRIG3 = "3"

PXI_TRIG4 = "4"

PXI_TRIG5 = "5"

PXI_TRIG6 = "6"

PXI_TRIG7 = "7"

# The system timing slot is slot 4, and the system

# timing set mapping to each peripheral slot is described.

[Chassis1StarSystemTimingSets1]

SystemTimingSlot = 4

StarSystemTimingSet0 = 4

StarSystemTimingSet1 = 2

StarSystemTimingSet2 = 3

[Chassis1StarTrigger1]

SystemTimingSlot = 4

PXI_STAR0 = 1

PXI_STAR1 = 2

PXI\_STAR2 = 3

PXI_STAR3 = 5

PXI_STAR4 = 6

PXI\_STAR5 = 7

PXI_STAR6 = 8

```

```

[Chassis1Slot1]

Model = "Example PXI Express System Model"

Vendor = "Example PXI Express System Vendor"

InstanceName = "Example PXI Express System Module, Instance 1"

AddressInfo = "SYSTEMMODULE::1"

SlotType = "PXIeSystemSlot4Link"

SystemSlotLinkWidth1 = 4

SystemSlotLinkWidth2 = 4

SystemSlotLinkWidth3 = 4

SystemSlotLinkWidth4 = 4

LocalBusRight = "Chassis1Slot2"

ControllerModuleLinkWidth1 = 1

ControllerModuleLinkWidth2 = 1

ControllerModuleLinkWidth3 = 1

ControllerModuleLinkWidth4 = 1

ControllerModuleType = "Remote"

SerialNumber = "699CWIK"

SubModel = "16CORE"

[Chassis1Slot2]

Model = "Example PXI Express Peripheral Model A"

Vendor = "Example PXI Express Peripheral Vendor"

InstanceName = "Example PXI Express Peripheral Module A, Instance 1"

AddressInfo = "PXI0::2-15.0::INSTR"

SlotType = "PXIePeripheralSlot"

SystemSlotLinkOrigin1 = 1

SystemSlotLinkOrigin2 = 0

PeripheralSlotLinkWidth1 = 4

PeripheralSlotLinkWidth2 = 0

LocalBusLeft = "Chassis1Slot1"

LocalBusRight = "Chassis1Slot3"

PeripheralModuleLinkWidthMax = 1

PeripheralModuleLinkWidthNegotiated = 1

PeripheralModuleOccupiedSlotList = "2,3"

[Chassis1Slot3]

SlotType = "PXIeHybridSlot"

SystemSlotLinkOrigin1 = 2

SystemSlotLinkOrigin2 = 4

PeripheralSlotLinkWidth1 = 4

PeripheralSlotLinkWidth2 = 0

LocalBusLeft = "Chassis1Slot2"

LocalBusRight = "Chassis1Slot4"

[Chassis1Slot4]

Model = "Example PXI Express System Timing Model B"

Vendor = "Example PXI Express System Timing Vendor"

InstanceName = "Example PXI Express System Timing Module B, Instance 1"

AddressInfo = "PXI0:::4-15.0::INSTR"

SlotType = "PXIeSystemTimingSlot"

SystemSlotLinkOrigin1 = 3

SystemSlotLinkOrigin2 = 0