# **PXI**<sup>TM</sup>-5

# PXI Express Hardware Specification

PCI EXPRESS eXtensions for Instrumentation

An Implementation of *CompactPCI®Express*

Revision 1.1 May 31, 2018

# IMPORTANT INFORMATION

#### Copyright

© Copyright 2005-2018 PXI Systems Alliance. All rights reserved.

This document is copyrighted by the PXI Systems Alliance. Permission is granted to reproduce and distribute this document in its entirety and without modification.

#### NOTICE

The *PXI Express Hardware Specification* is authored and copyrighted by the PXI Systems Alliance. The intent of the PXI Systems Alliance is for the *PXI Express Hardware Specification* to be an open industry standard supported by a wide variety of vendors and products. Vendors and users who are interested in developing PXI-compatible products or services, as well as parties who are interested in working with the PXI Systems Alliance to further promote PXI as an open industry standard are invited to contact the PXI Systems Alliance for further information.

The PXI Systems Alliance wants to receive your comments on this specification. Visit the PXI Systems Alliance web site at http://www.pxisa.org/ for contact information and to learn more about the PXI Systems Alliance.

The attention of adopters is directed to the possibility that compliance with or adoption of the PXI Systems Alliance specifications may require use of an invention covered by patent rights. The PXI Systems Alliance shall not be responsible for identifying patents for which a license may be required by any PXI Systems Alliance specification, or for conducting legal inquiries into the legal validity or scope of those patents that are brought to its attention. PXI Systems Alliance specifications are prospective and advisory only. Prospective users are responsible for protecting themselves against liability for infringement of patents.

The information contained in this document is subject to change without notice. The material in this document details a PXI Systems Alliance specification in accordance with the license and notices set forth on this page. This document does not represent a commitment to implement any portion of this specification in any company's products.

The PXI Systems Alliance makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The PXI Systems Alliance shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Compliance with this specification does not absolve manufacturers of PXI equipment from the requirements of safety and regulatory agencies (UL, CSA, FCC, IEC, etc.).

#### **Trademarks**

PXI<sup>TM</sup> is a trademark of the PXI Systems Alliance.

PICMG<sup>TM</sup> and CompactPCI<sup>®</sup> are trademarks of the PCI Industrial Computation Manufacturers Group.

Product and company names are trademarks or trade names of their respective companies.

# PXI Express Hardware Specification Revision History

This section is an overview of the revision history of the PXI Express Hardware Specification.

#### **Revision 1.0, August 22, 2005**

This is the first public revision of the PXI Express specification.

#### **Revision 1.1, May 31, 2018**

- Allowed PXI Express Peripheral Modules and System Timing Modules to draw 3 A/pin on 12 V and 3.3 V.

- Allowed PXI Express System Modules to draw 15 A/pin on 12 V, 5 V, and 3.3 V up to a maximum of 45 A.

- Added recommendation for modules to have thermal protection.

- Updated maximum bandwidth numbers in overview sections factoring in Gen 3 PCI Express performance.

- Incorporated relevant aspects of PXI Express Hardware Specification ECN 1 revision 2.0, making the ECN 1 obsolete.

This Page Intentionally Left Blank

# **Contents**

| 1. | Introduc      | tion     |                |                                                          |    |

|----|---------------|----------|----------------|----------------------------------------------------------|----|

|    | 1.1           | Objecti  | ives           |                                                          | 11 |

|    | 1.2           | Intende  | ed Audience    | and Scope                                                | 13 |

|    | 1.3           | Backgr   | ound and Te    | rminology                                                | 13 |

|    | 1.4           | Applic   | able Docume    | ents                                                     | 14 |

|    | 1.5           | Useful   | Web Sites      |                                                          | 14 |

| 2. | PXI Exp       | ress Ard | chitecture (   | Overview                                                 |    |

|    | 2.1           | Mecha    | nical Archite  | cture Overview                                           | 17 |

|    |               | 2.1.1    |                | nd Slot Types                                            |    |

|    |               |          | 2.1.1.1        | 3U and 6U PXI Express System Module and Slot             |    |

|    |               |          | 2.1.1.2        | 3U and 6U PXI Express Peripheral Module and Slot         |    |

|    |               |          | 2.1.1.3        | 3U and 6U PXI Express Hybrid Peripheral Slot             |    |

|    |               |          | 2.1.1.4        | 3U and 6U PXI Express System Timing Module and Slot      |    |

|    |               |          | 2.1.1.5        | PXI-1 Slot                                               |    |

|    |               |          | 2.1.1.6        | 3U and 6U Hybrid Slot Compatible PXI-1 Peripheral Module | 28 |

|    |               | 2.1.2    | System Sl      | ot and System Timing Module Location                     | 29 |

|    |               | 2.1.3    | Additiona      | l Mechanical Features                                    | 30 |

|    |               | 2.1.4    | Interopera     | bility with CompactPCI Express                           | 30 |

|    |               | 2.1.5    |                | ystem Components                                         |    |

|    |               | 2.1.6    | Chassis St     | upporting Stacking 3U Modules in a 6U Slot               | 31 |

|    | 2.2           | Electric | cal Architectu | ure Overview                                             | 32 |

|    |               | 2.2.1    |                | Leveraged from CompactPCI Express                        |    |

|    |               | 2.2.2    |                | everaged from the PXI Hardware Specification             |    |

|    |               | 2.2.3    |                | umentation Features                                      |    |

|    |               |          | 2.2.3.1        | High-Frequency System Reference Clock                    |    |

|    |               |          | 2.2.3.2        | Differential Synchronization Signal                      |    |

|    |               |          | 2.2.3.3        | Differential Triggers                                    |    |

|    |               | 224      | 2.2.3.4        | System Timing Module                                     |    |

|    |               | 2.2.4    |                | ification                                                |    |

|    |               |          | 2.2.4.1        | Module Drivers and the GA Pins                           |    |

|    |               | 225      | 2.2.4.2        | Determining the Chassis Number                           |    |

|    |               | 2.2.5    |                | dentification                                            |    |

|    |               | 2.2.6    |                | lentification                                            |    |

|    | 2.3           | 2.2.7    |                | quirements                                               |    |

| _  |               |          |                |                                                          | 30 |

| 3. | Mechan<br>3.1 |          | quirements     | <b>.</b>                                                 | 41 |

|    | 3.1           |          | -              |                                                          |    |

|    | 3.3           |          |                | echanical Requirements                                   |    |

|    | 3.4           |          |                | uirements to be a PXI Express Chassis                    |    |

|    | 3.5           |          |                | from PXI-1: PXI Hardware Specification                   |    |

|    | 3.3           | 3.5.1    |                | Number of Slots                                          |    |

|    |               | 3.5.2    |                | ot Location and Rules                                    |    |

|    |               | 3.5.3    | •              | bering and Orientation                                   |    |

|    |               | 3.5.4    |                | t                                                        |    |

|    |               | 3.5.5    |                | ot-Compatible PXI-1 Peripheral Modules                   |    |

|    | 3.6           |          | •              | from CompactPCI Express Specification                    |    |

|    | 5.0           | 3.6.1    | _              | onnector Requirements                                    |    |

|    |               | 1        | 3.6.1.1        | Advanced Differential Fabric (ADF) Connector             |    |

|    |               |          | 3.6.1.2        | Enriched Hard-Metric (eHM) Connector                     |    |

|    |               |          | 3.6.1.3        | Universal Power (UPM) Connector                          |    |

|              |           | 3.6.2    | Backplan      | e Connector Requirements                     | 43 |

|--------------|-----------|----------|---------------|----------------------------------------------|----|

|              |           |          | 3.6.2.1       | Advanced Differential Fabric (ADF) Connector | 43 |

|              |           |          | 3.6.2.2       | Enriched Hard-Metric (eHM) Connector         | 43 |

|              |           |          | 3.6.2.3       | Universal Power (UPM) Connector              | 43 |

|              |           | 3.6.3    | 3U and 6      | U Module Requirements                        | 44 |

|              |           |          | 3.6.3.1       | System Module                                |    |

|              |           |          | 3.6.3.2       | PXI Express Peripheral Module                | 44 |

|              |           | 3.6.4    | Backplan      | e Requirements                               | 46 |

|              |           |          | 3.6.4.1       | System Slot                                  | 46 |

|              |           |          | 3.6.4.2       | Peripheral Slot                              |    |

|              |           |          | 3.6.4.3       | PXI Express Hybrid Peripheral Slot           |    |

|              | 3.7       | New M    |               | lot Types                                    |    |

|              |           | 3.7.1    |               | ess System Timing Module Requirements        |    |

|              |           | 3.7.2    | Backplan      | e Requirements for New Slot Types            |    |

|              |           |          | 3.7.2.1       | PXI Express System Timing Slot Requirements  |    |

|              | 3.8       | Require  | ements for S  | tacking 3U Modules in 6U Slots               | 54 |

|              | 3.9       |          |               |                                              |    |

|              | 3.10      | Chassis  | s with Built- | In System Modules                            | 55 |

|              | 3.11      |          |               | ents                                         |    |

|              |           | 3.11.1   |               | Cooling Requirements                         |    |

|              |           | 3.11.2   |               | Cooling Requirements                         |    |

|              | 3.12      | Enviro   |               | cifications                                  |    |

|              |           | 3.12.1   |               | ure Specifications                           |    |

|              |           | 3.12.2   | •             | Specifications                               |    |

|              |           | 3.12.3   |               | Specifications                               |    |

|              |           | 3.12.4   |               | Noise Specifications                         |    |

|              | 3.13      | PXI Ex   | -             | atibility Glyphs                             |    |

|              |           | 3.13.1   |               | Glyphs                                       |    |

|              |           | 3.13.2   | Chassis S     | lot Glyphs                                   | 58 |

| <b>4</b> . I | Electrica | al Requi | irements      |                                              |    |

|              | 4.1       | -        |               |                                              | 50 |

|              | 7.1       | 4.1.1    |               | lot Requirements                             |    |

|              |           | 4.1.2    | •             | ot Requirements                              |    |

|              | 4.2       |          |               | als                                          |    |

|              | 2         | 4.2.1    |               | Iodule/Slot Requirements                     |    |

|              |           | 4.2.2    |               | ess Peripheral Module / Slot Requirements    |    |

|              |           | 4.2.3    |               | iming Module/Slot Requirements               |    |

|              |           | 4.2.4    |               | lot Requirements                             |    |

|              | 4.3       |          |               | ion Signals                                  |    |

|              |           | 4.3.1    |               | e Clock: PXI_CLK10                           |    |

|              |           | 4.3.2    |               | us                                           |    |

|              |           | 4.3.3    |               | ger                                          |    |

|              |           | 4.3.4    |               | S                                            |    |

|              | 4.4       |          |               | g References                                 |    |

|              |           | 4.4.1    | -             | e Requirements                               |    |

|              |           | •        | 4.4.1.1       | PXIe_CLK100                                  |    |

|              |           |          | 4.4.1.2       | PXI_CLK10                                    |    |

|              |           |          | 4.4.1.3       | PXIe_SYNC100                                 |    |

|              |           |          | 4.4.1.4       | Timing, Switching, and PXIe_SYNC_CTRL        |    |

|              |           | 4.4.2    | System T      | iming Module Requirements                    |    |

|              |           | 4.4.3    | •             | l Module Requirements                        |    |

|              |           |          | 4.4.3.1       | PXIe CLK100                                  |    |

|            |          |          | 4.4.3.2        | PXI_CLK10                                     | 72 |

|------------|----------|----------|----------------|-----------------------------------------------|----|

|            |          |          | 4.4.3.3        | PXIe_SYNC100                                  | 72 |

|            | 4.5      | Differen | ntial Triggers | S                                             | 74 |

|            |          | 4.5.1    | Chassis Re     | equirements                                   | 74 |

|            |          | 4.5.2    | PXIe Perip     | pheral Module / Slot Requirements             | 75 |

|            |          |          | 4.5.2.1        | PXIe_DSTARA                                   | 75 |

|            |          |          | 4.5.2.2        | PXIe_DSTARB                                   |    |

|            |          |          | 4.5.2.3        | PXIe_DSTARC                                   | 76 |

|            |          | 4.5.3    | System Ti      | ming Module/Slot Requirements                 |    |

|            |          |          | 4.5.3.1        | PXIe_DSTARA                                   |    |

|            |          |          | 4.5.3.2        | PXIe_DSTARB                                   |    |

|            |          |          | 4.5.3.3        | PXIe_DSTARC                                   |    |

|            | 4.6      |          |                |                                               |    |

|            | 4.7      |          |                | ition                                         |    |

|            | 4.8      |          |                | servation                                     |    |

|            | 4.9      |          |                | s for 6U                                      |    |

|            |          | 4.9.1    |                | s that Support Stacking 3U Modules            |    |

|            | 4.10     |          |                | nments                                        |    |

|            |          | 4.10.1   |                | ss Peripheral Slots and Modules               |    |

|            |          | 4.10.2   | -              | ss System Slot and Modules                    |    |

|            |          |          | 4.10.2.1       | 4 Link Configuration                          |    |

|            |          |          | 4.10.2.2       | 2 Link Configuration                          |    |

|            |          | 4.10.3   | -              | ss Hybrid Peripheral Slot                     |    |

|            |          | 4.10.4   |                | t                                             |    |

|            |          | 4.10.5   | •              | ming Slot                                     |    |

|            |          | 4.10.6   |                | Connector Pin Assignments                     |    |

|            | 4.11     |          |                |                                               |    |

|            |          | 4.11.1   |                | quirements from CompactPCI Express            |    |

|            |          | 4.11.2   |                | equirements                                   |    |

|            |          |          | 4.11.2.1       | Chassis Minimum Required Continuous Current   |    |

|            |          |          | 4.11.2.2       | Low-Power Chassis Power Supply Specifications |    |

|            |          | 4.11.3   |                | equirements                                   |    |

|            | 4.40     | <i>a</i> | 4.11.3.1       | Module Maximum Continuous Current Draw        |    |

|            | 4.12     | Chassis  | Grounding.     |                                               | 88 |

| _          | Danulak  | D.a      |                |                                               |    |

| <b>5</b> . | Regulati |          | uirements      |                                               |    |

|            | 5.1      | Require  | ements for El  | MC                                            | 89 |

|            | 5.2      |          |                | ectrical Safety                               |    |

|            | 5.3      | Additio  | nal Requiren   | nents for Chassis                             | 89 |

|            |          |          | _              |                                               |    |

| 6.         | PXI Expr | ess Sof  | tware Spec     | cification Compliance                         |    |

|            |          |          |                |                                               |    |

| Fig        | ures     |          |                |                                               |    |

|            | Figur    | e 1-1.   | PXI Express    | Hardware Specification Architectures          | 12 |

|            | Figur    |          | _              | S Software Specification Architecture         |    |

|            | Figur    |          |                | ress System Module                            |    |

|            | Figur    |          | _              | ress System Module                            |    |

|            | Figur    |          | _              | ress System Slot                              |    |

|            | Figur    |          |                | ress System Slot                              |    |

|            | Figur    |          |                | ress Peripheral Module                        |    |

|            | Figur    |          |                | ress Peripheral Module                        |    |

|            | Figur    |          | _              | ress Peripheral Slot                          |    |

|            | Figur    |          | -              | ress Peripheral Slot                          |    |

|            | _        |          | 1              | <u>*</u>                                      |    |

|        | Figure 2-9.  | 3U PXI Express Hybrid Peripheral Slot                                       | 24 |

|--------|--------------|-----------------------------------------------------------------------------|----|

|        | Figure 2-10. | 6U PXI Express Hybrid Peripheral Slot                                       | 25 |

|        | Figure 2-11. | 6U PXI Express System Timing Module                                         | 26 |

|        | Figure 2-12. | 3U PXI Express System Timing Slot                                           | 27 |

|        | Figure 2-13. | 6U PXI Express System Timing Slot                                           | 27 |

|        | Figure 2-14. | 6U PXI Express System Timing Slot with Stacked 3U Support                   | 28 |

|        | Figure 2-15. | 3U Hybrid Peripheral Slot Compatible PXI-1 Module                           | 29 |

|        | Figure 2-16. | 6U Hybrid Peripheral Slot Compatible PXI-1 Module                           | 29 |

|        | Figure 2-17. | Typical System Components                                                   | 31 |

|        | Figure 2-18. | Example of a PXI Express Chassis that Supports 3U Stacking                  | 32 |

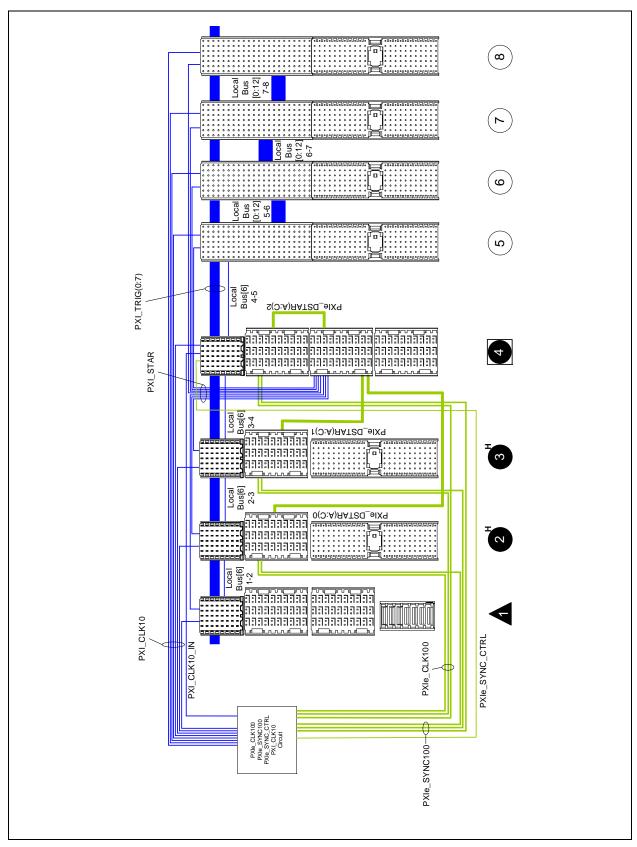

|        | Figure 2-19. | Instrumentation Signal Implementation Example                               | 35 |

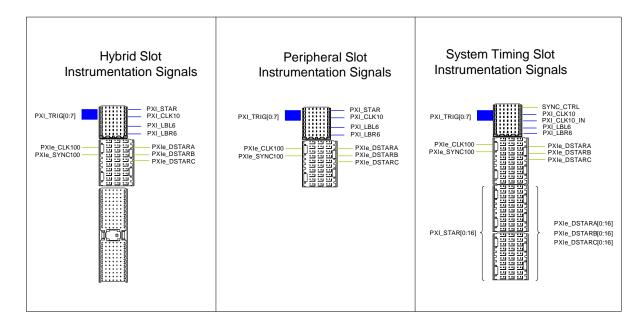

|        | Figure 2-20. | Instrumentation Signals Connector Mapping.                                  | 36 |

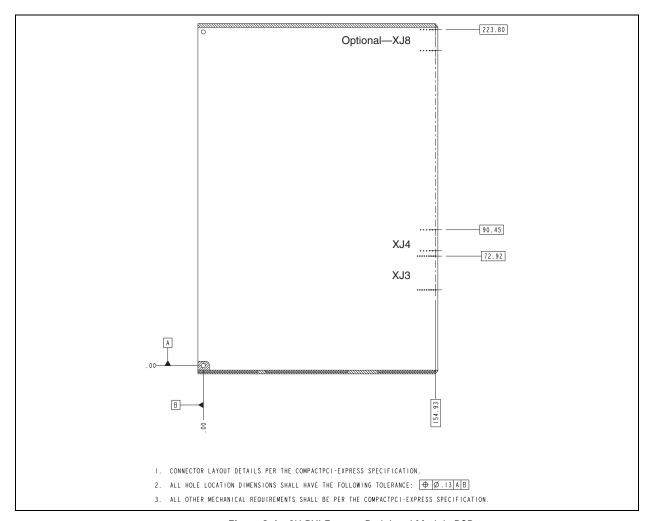

|        | Figure 3-1.  | 6U PXI Express Peripheral Module PCB                                        | 45 |

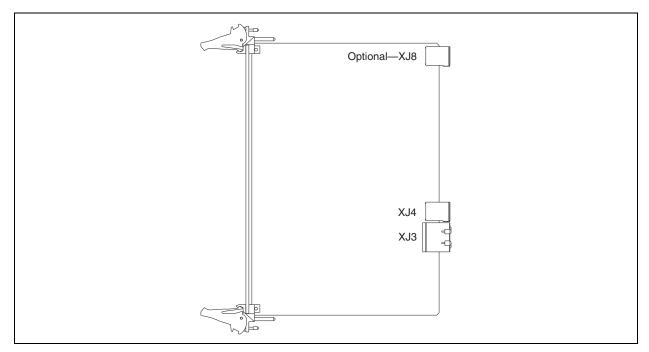

|        | Figure 3-2.  | 6U PXI Express Peripheral Module                                            | 46 |

|        | Figure 3-3.  | 6U PXI Express Peripheral Slot                                              | 47 |

|        | Figure 3-4.  | 6U PXI Express Hybrid Slot                                                  |    |

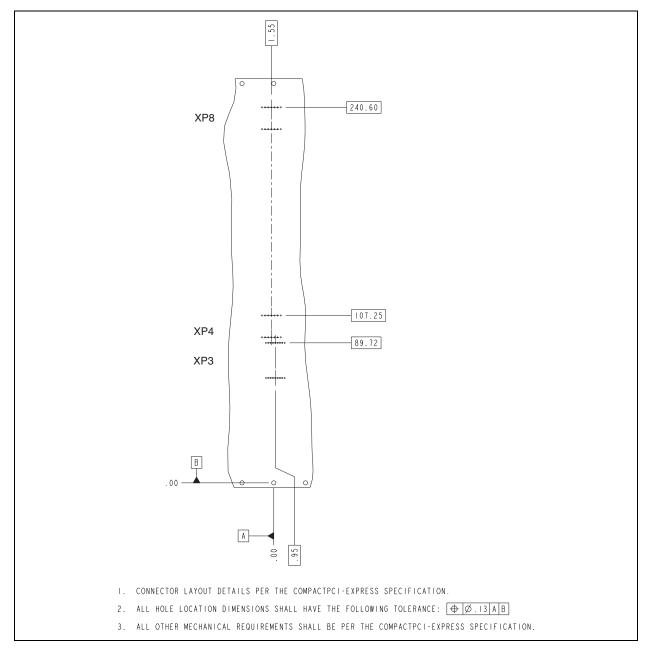

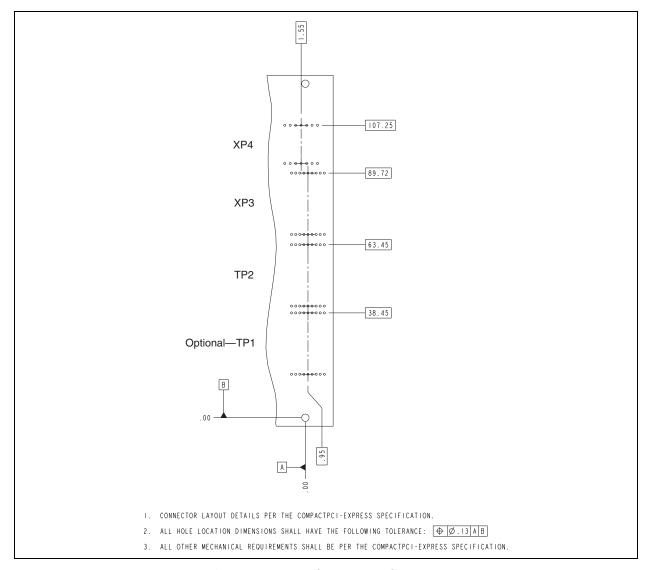

|        | Figure 3-5.  | 3U PXI Express System Timing Module PCB                                     | 49 |

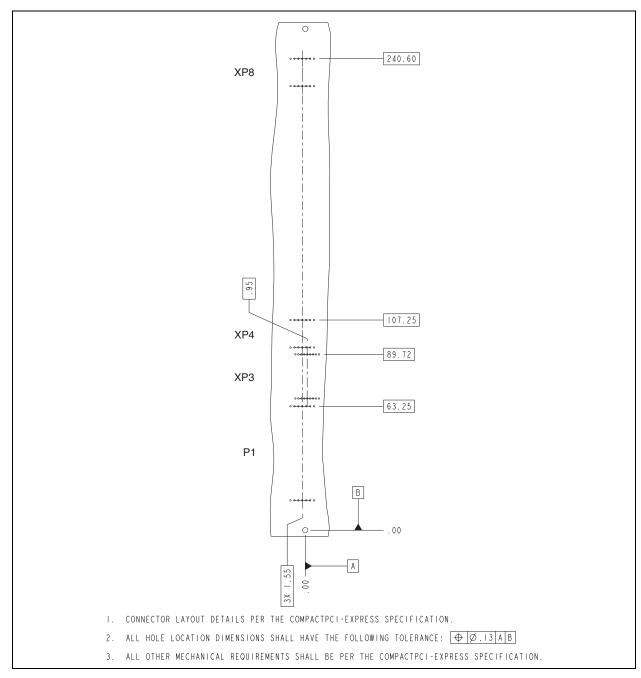

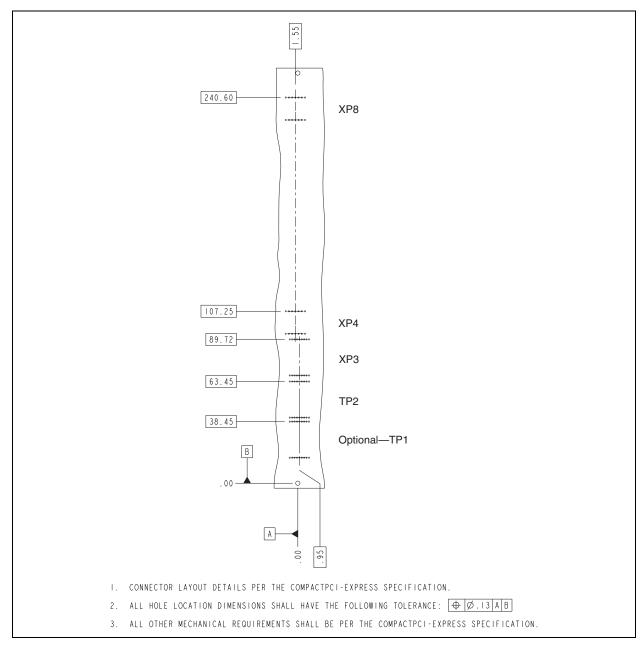

|        | Figure 3-6.  | 6U PXI Express System Timing Module PCB                                     |    |

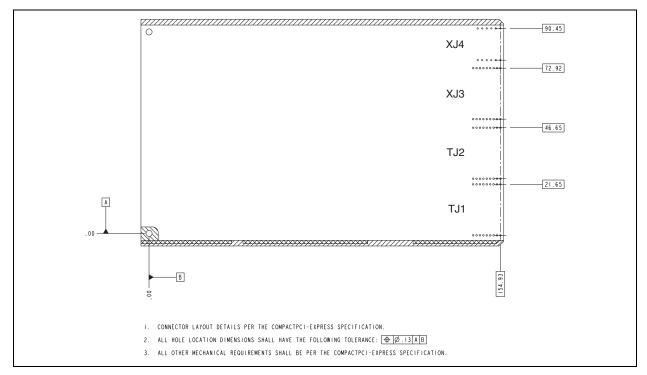

|        | Figure 3-7.  | 3U PXI Express System Timing Slot Backplane Dimensions                      | 51 |

|        | Figure 3-8.  | 6U PXI Express System Timing Slot Backplane Dimensions                      | 52 |

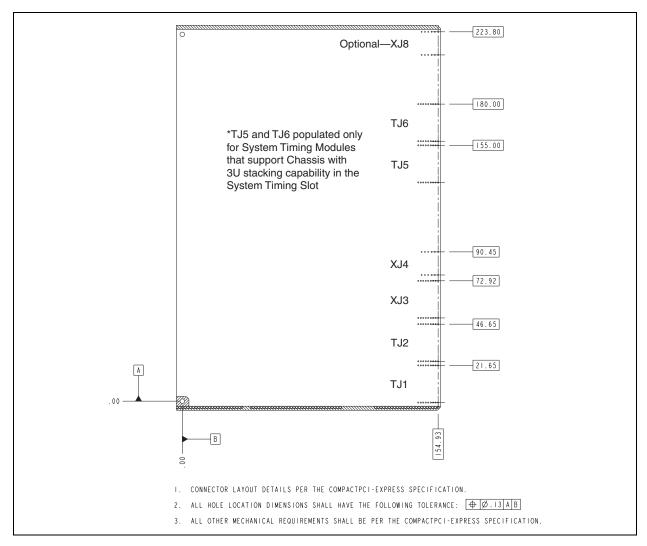

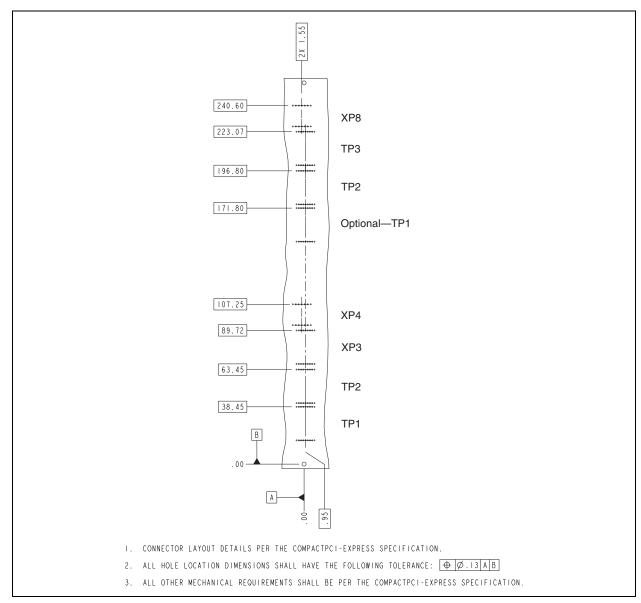

|        | Figure 3-9.  | 6U PXI Express System Timing Slot with Stacked Support Backplane Dimensions | 53 |

|        | Figure 3-10. | PXI Logo                                                                    | 55 |

|        | Figure 3-11. | PXI Express Logo                                                            |    |

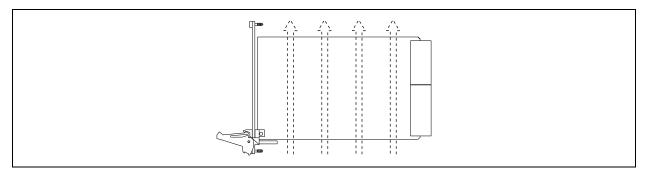

|        | Figure 3-12. | Cooling Airflow Direction in a PXI Express System                           | 56 |

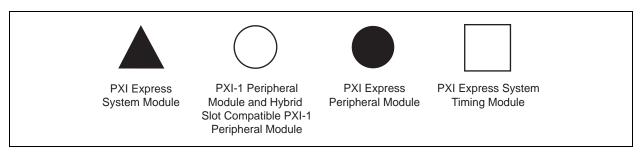

|        | Figure 3-13. | Module Glyphs                                                               | 58 |

|        | Figure 3-14. | Slot Glyphs                                                                 |    |

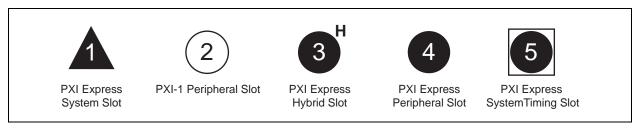

|        | Figure 4-1.  | PXI Trigger Bus Termination                                                 |    |

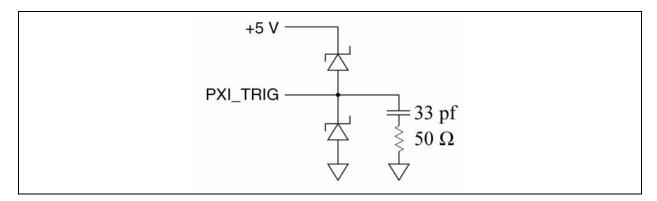

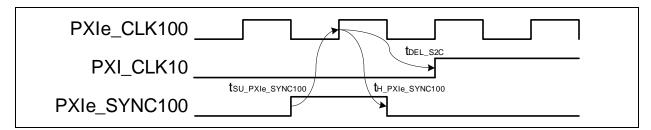

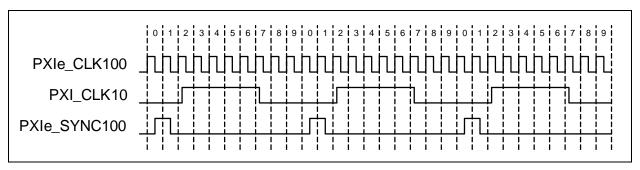

|        | Figure 4-2.  | Timing relationship of PXI_CLK10 to PXIe_CLK100                             |    |

|        | Figure 4-3.  | Timing Relationship of PXIe_SYNC100 to PXI_CLK10 and PXIe_CLK100            | 68 |

|        | Figure 4-4.  | PXIe_SYNC100 Default Behavior                                               |    |

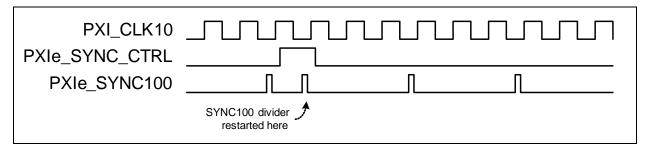

|        | Figure 4-5.  | PXIe_SYNC100 at 3.33 MHz Using PXIe_SYNC_CTRL as Restart                    |    |

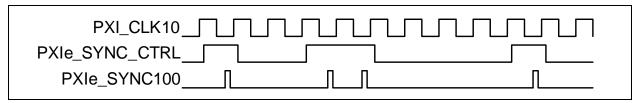

|        | Figure 4-6.  | PXIe_SYNC100 Using PXIe_SYNC_CTRL as Enable                                 |    |

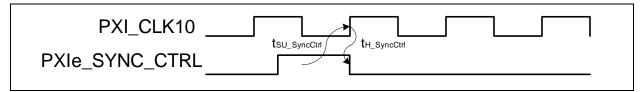

|        | Figure 4-7.  | Timing Relationship between SYNC_CTRL and PXI_CLK10                         |    |

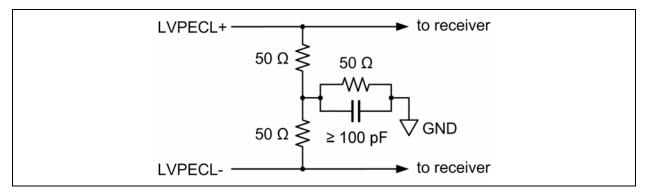

|        | Figure 4-8.  | Peripheral Module Circuit for Terminating PXIe_CLK100 Signal                |    |

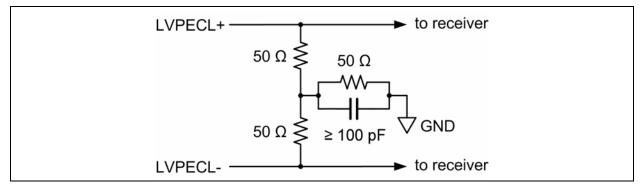

|        | Figure 4-9.  | Peripheral Module Circuit for Terminating PXIe_SYNC100 Circuit              |    |

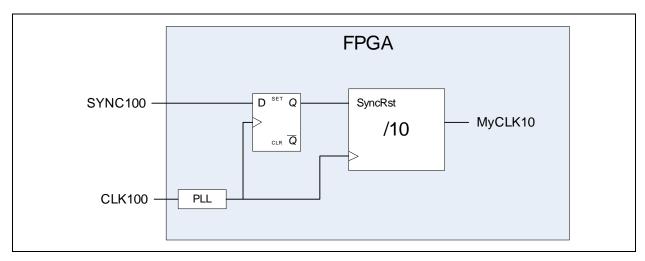

|        | Figure 4-10. | Circuit to recreate PXI_CLK10 Internally as MyCLK10                         |    |

|        | Figure 4-11. | Peripheral Module Circuit for Terminating PXIe_DSTARA                       |    |

|        | Figure 4-12. | Text Required for Low-Power Chassis                                         | 88 |

|        |              |                                                                             |    |

| Tables | 8            |                                                                             |    |

|        | Table 2-1.   | PXI Express and CompactPCI Express Specification Names                      |    |

|        | Table 2-2.   | PXI and PXI Express Module Interoperability                                 | 33 |

|        | Table 3-1.   | Upper and Lower 3U Slot Implementation                                      |    |

|        | Table 4-1.   | System Module and Slot Requirements                                         |    |

|        | Table 4-2.   | PXI Express Peripheral Module and Slot Requirements                         | 61 |

|        | Table 4-3.   | System Timing Module and Slot Requirements                                  | 62 |

|        | Table 4-4.   | Hybrid Slot Requirements                                                    |    |

|        | Table 4-5.   | Timing relationship of PXI_CLK10 to PXIe_CLK100                             |    |

|        | Table 4-6.   | Timing Relationship of PXIe_SYNC100 to PXI_CLK10 and PXIe_CLK100            |    |

|        | Table 4-7.   | Timing Relationship between SYNC_CTRL and PXI_CLK10                         |    |

|        | Table 4-8.   | PXIe_DSTAR Set Mapping                                                      |    |

|        | Table 4-9.   | PXI Express Peripheral Slot and Module Pin Assignments                      |    |

|        | Table 4-10.  | Pin Assignments for 4 Link Operation.                                       | 81 |

| Table 4-11. | Pin Assignments for 2 Link Operation                    | . 82 |

|-------------|---------------------------------------------------------|------|

| Table 4-12. | Hybrid Peripheral Slot Pin Assignments                  | . 83 |

| Table 4-13. | PXI Express System Timing Slot/Module Pinout            | . 84 |

| Table 4-14. | XP8/XJ8 Pin Assignments                                 | . 85 |

| Table 4-15. | PXI Express Chassis Minimum Required Continuous Current | . 86 |

| Table 4-16. | PXI Express Backplane Continuous Current Capability     | . 87 |

This Page Intentionally Left Blank

# 1. Introduction

This section describes the primary objectives and scope of the PXI-5: PCI Express eXtensions for Instrumentation specification. It also defines the intended audience and lists relevant terminology and documents.

# 1.1 Objectives

PXI Express was created to build on the successful PXI-1: PXI Hardware Specification and the new CompactPCI Express standard to make new levels of performance possible in modular instrumentation and automation Systems. Similar to the PXI-1 standard, existing industry standards are leveraged by PXI Express to benefit from high component availability at lower costs. PXI Express also continues to maintain software compatibility with industry-standard personal computers, allowing customers to use the same software tools and environments with which they are familiar. Not only does PXI Express provide a giant leap in measurement and automation performance, but it also provides a high level of compatibility with PXI-1, so customers can preserve their investment in PXI-1 Modules.

PXI Express leverages the electrical features defined by the widely adopted PCI Express specification for data movement. This is accomplished by PXI Express Modules complying with the CompactPCI Express specification, which combines the PCI Express electrical specification with rugged Eurocard mechanical packaging and high-performance differential connectors. This allows measurement and automation Systems based on PXI Express to have a data throughput of upto 128 GBytes/sec in each direction. PXI Express also offers two-way interoperability with CompactPCI Express products.

Instrumentation capabilities within PXI Express can reach a new level of performance by providing point-to-point differential triggers, point-to-point differential variable clocks, and a 100 MHz differential System clock. The highly used bussed triggers, point-to-point triggers, and 10 MHz clock defined in the PXI-1 specification are maintained. This allows PXI Express Module designers to make optimized cost versus performance tradeoffs when implementing instrumentation features.

PXI Express maintains compatibility with Modules designed to be compliant with the PXI-1 specification in two ways. First, PXI Express allows Chassis to have slots that are defined in the PXI-1 specification. Second, PXI Express defines a slot that accepts either a high-performance Module that uses PCI Express for data transfer or a Module designed to the PXI-1 specification that has had a connector change. Of course, this also means PXI Express allows for the compatibility with Modules designed to the CompactPCI specification.

By implementing PCI Express, PXI Express Systems can leverage the large base of existing industry-standard software. Desktop PC users have access to different levels of software, from operating systems to low-level device drivers to high-level instrument drivers to complete graphical APIs. All of these software levels can be used in PXI Express Systems. The PXI Systems Alliance maintains a separate Software Specification for PXI Express Modules, Chassis, and Systems. By having a separate Software Specification, the PXI Systems Alliance can more quickly adopt the latest operating Systems and software standards. PXI Express Modules, Chassis, and Systems developed to comply with this PXI Hardware Specification must also comply with the PXI-6: *PXI Express Software Specification*.

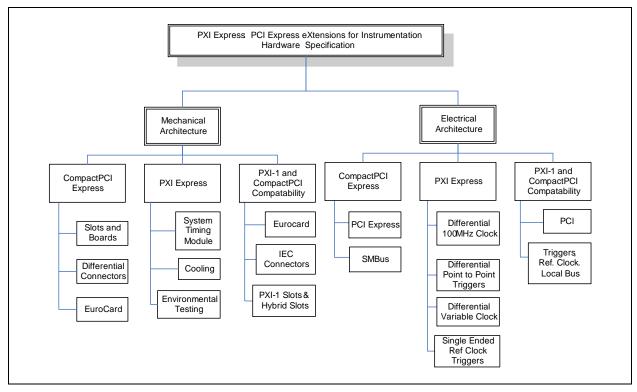

Figure 1-1 summarizes the scope of the *PXI Express Hardware Specification* by depicting its mechanical and electrical architectures.

Figure 1-1. PXI Express Hardware Specification Architectures

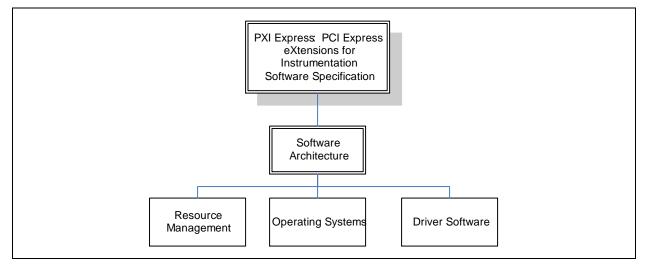

Figure 1-2 summarizes the scope of the PXI-6: PXI Express Software Specification by depicting its architecture.

Figure 1-2. PXI Express Software Specification Architecture

# 1.2 Intended Audience and Scope

This specification is organized with a top-down approach whereby general descriptions precede the more detailed specifications found deeper in the subsections. This structure is intended to serve the needs of a variety of audiences from product developers to System integrators to end-users. Product developers may want to become familiar with all portions of this specification, while end users may be interested in only the feature set description and perhaps the summaries of how these features are implemented. The goal of this specification is to serve as the highest level document relevant to all users and providers of PXI Express compatible Systems, but in many cases this specification references other specifications such as CompactPCI Express and PXI-1 for certain details. These specifications and the specifications they in turn refer to may be needed to fully implement PXI Express products.

The first section of this specification describes the features that PXI Express Systems can offer and how these features can be applied to instrumentation. The subsequent sections cover the mechanical, electrical, and software requirements specific to implementing PXI Express features.

# 1.3 Background and Terminology

This section defines the acronyms and key words that are referred to throughout this specification. This specification uses the following acronyms:

- API—Application Programming Interface

- CompactPCI—PICMG 2.0 Specification

- **Eurocard**—European Packaging Specifications (IEC 60297, IEEE 1101.1, IEEE 1101.10, IEEE 1101.11)

- **GPIB**—General Purpose Interface Bus, IEEE 488

- ISA—Industry Standard Architecture; desktop PC adapter board specification

- PCI—Peripheral Component Interconnect; electrical specification defined by PCISIG

- PCI Express—Serialized evolution of PCI

- **PCI-SIG**—PCI Special Interest Group

- PICMG—PCI Industrial Computer Manufacturers Group

- **PXI**—PCI eXtensions for Instrumentation

- PXI Express—PCI Express eXtensions for Instrumentation

- VISA—Virtual Instrument Software Architecture

- VITA—VMEbus International Trade Association

- VME—Versa Module Europe; VMEbus specification governed by the VSO

- VPP—VXIplug&play Specification

- VSO—VITA Standards Organization

- VXI—VME Extensions for Instrumentation

This specification uses several key words, which are defined as follows:

**RULE:** Rules SHALL be followed to ensure compatibility. A rule is characterized by the use of the words SHALL and SHALL NOT.

**RECOMMENDATION:** Recommendations consist of advice to implementers that will affect the usability of the final Module. A recommendation is characterized by the use of the words SHOULD and SHOULD NOT.

**PERMISSION:** Permissions clarify the areas of the specification that are not specifically prohibited. Permissions reassure the reader that a certain approach is acceptable and will cause no problems. A permission is characterized by the use of the word MAY.

**OBSERVATION:** Observations spell out implications of rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules, so that the reader understands why the rule must be followed.

**MAY:** A key word indicating flexibility of choice with no implied preference. This word is usually associated with a permission.

**SHALL:** A key word indicating a mandatory requirement. Designers SHALL implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification. This word is usually associated with a rule.

**SHOULD:** A key word indicating flexibility of choice with a strongly preferred implementation. This word is usually associated with a recommendation.

# 1.4 Applicable Documents

This specification defines extensions to the base PCI Express and CompactPCI Express specifications referenced in this section. It is assumed that the reader has a thorough understanding of PCI Express and CompactPCI Express. The CompactPCI Express specification refers to several other applicable documents with which the reader may wish to become familiar. This specification refers to the following documents directly:

- PXI Software Specification (Latest Revision)

- PXI Hardware Specification (Latest Revision)

- PCI Local Bus Specification, Rev. 2.3

- PCI Express Base Specification 1.1

- PCI Express Card Electromechanical (CEM) Specification 1.1

- PICMG 2.0 R3.0 CompactPCI Specification

- PICMG EXP.0 CompactPCI Express Specification

- System Management Bus (SMBus) Specification, Version 2.0

- VXI*plug&play* Specifications (VPP-3.x and VPP-7)

- IEC 61326-1:1998, Electrical equipment for measurement, control, and laboratory use—EMC requirements—Part I, General requirements, International Electrotechnical Commission

- IEC 1010-1:1990 + A1:1992, Safety requirements for electrical equipment for measurement, control, and laboratory use—Part 1, General requirements, International Electrotechnical Commission

- IEC 60068-1, Environmental testing, International Electrotechnical Commission

# 1.5 Useful Web Sites

Below is a list of Web site links that at the time of publication of this specification point to sites with information useful in the understanding and design of PXI products:

- http://www.pxisa.org/—PXI specifications

- http://www.picmg.org/—PICMG specifications

- http://www.ieee.org/—IEEE specifications

- http://www.iec.org/—IEC specifications

- http://www.pcisig.com/—PCI and PCI Express specifications

- http://www.vita.com/—VME specifications

- http://www.vxi.org/—VXI specifications

- http://www.vxipnp.org/—VISA specifications

- http://www.smbus.org/—SMBus specification

This Page Intentionally Left Blank

# 2. PXI Express Architecture Overview

This section presents an overview of PXI Express System features and capabilities by summarizing the mechanical, electrical, and software architectures defined by this specification.

# 2.1 Mechanical Architecture Overview

PXI Express supports 3U and 6U Module form factors just like PXI-1. Several new connectors have been added to support PCI-Express and are defined by the CompactPCI Express specification. This specification uses different names for the Module and slot types as compared to CompactPCI Express and introduces some new types as well. Table 2-1 shows the PXI Express component name and the equivalent CompactPCI Express component name.

Table 2-1. PXI Express and CompactPCI Express Specification Names

| PXI Express Specification Name      | CompactPCI Express Specification Name |  |  |  |

|-------------------------------------|---------------------------------------|--|--|--|

| PXI Express System Slot             | System Slot                           |  |  |  |

| PXI Express System Module           | System Board                          |  |  |  |

| PXI Express Peripheral Slot         | Type 2 Peripheral Slot                |  |  |  |

| PXI Express Peripheral Module       | Type 2 Peripheral Board               |  |  |  |

| PXI Express Hybrid Slot             | Hybrid Slot                           |  |  |  |

| Hybrid Slot Compatible PXI-1 Module | N/A                                   |  |  |  |

| PXI Express System Timing Slot      | N/A                                   |  |  |  |

| PXI Express System Timing Module    | N/A                                   |  |  |  |

| PXI-1 Slot                          | Legacy Slot                           |  |  |  |

| PXI-1 Module                        | CompactPCI Peripheral Board           |  |  |  |

The Module and slot types used from the CompactPCI Express specification as well as the new ones introduced by this specification are described in the following sections.

# 2.1.1 Module and Slot Types

PXI Express Module and slot types include a 3U and 6U PXI Express System Module and Slot, a 3U and 6U PXI Express Peripheral Module and Slot, a PXI Express 3U and 6U Hybrid Peripheral Slot, a 3U and 6U PXI Express System Timing Module and Slot, a 3U and 6U Hybrid Slot, and a 3U and 6U Hybrid Slot compatible PXI-1 Module. In addition to these Module and slot types, 3U and 6U PXI Peripheral Slots defined in the PXI-1 specification are allowed in PXI Express Chassis to support PXI-1 Peripheral Modules.

# 2.1.1.1 3U and 6U PXI Express System Module and Slot

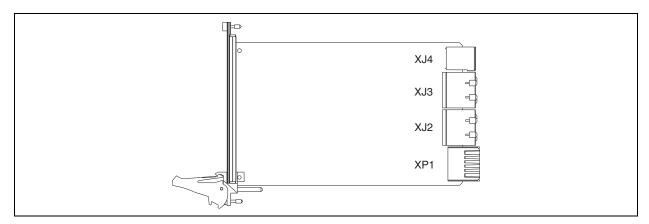

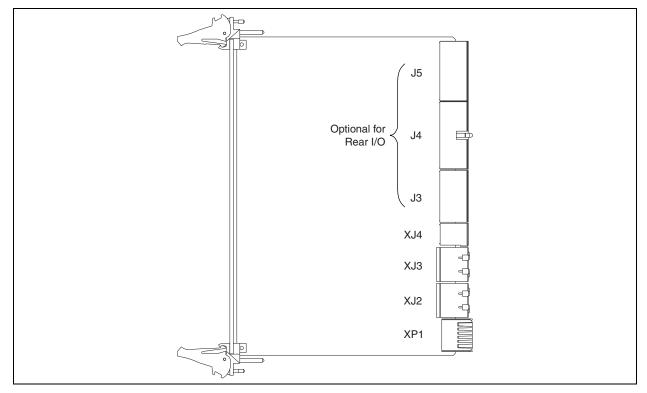

PXI Express System Modules have four required connectors, XP1/XJ2/XJ3/XJ4, as defined by the CompactPCI Express specification. A simplified description of the connector functionality is XP1/XJ1 is for power, XP2/XJ2 and XP3/XJ3 are for PCI Express, and XP4/XJ4 is for instrumentation signals defined in the PXI-1 specification. The 6U System Module may use J3/J4/J5 for rear I/O applications.

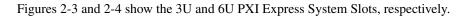

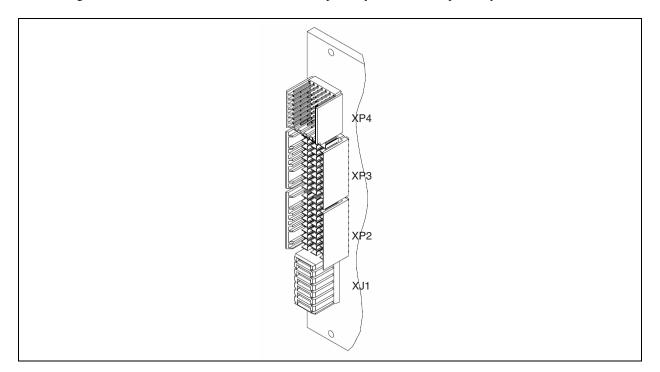

Figures 2-1 and 2-2 show the 3U and 6U PXI Express System Modules, respectively.

Figure 2-1. 3U PXI Express System Module

Figure 2-2. 6U PXI Express System Module

Figure 2-3. 3U PXI Express System Slot

Figure 2-4. 6U PXI Express System Slot

# 2.1.1.2 3U and 6U PXI Express Peripheral Module and Slot

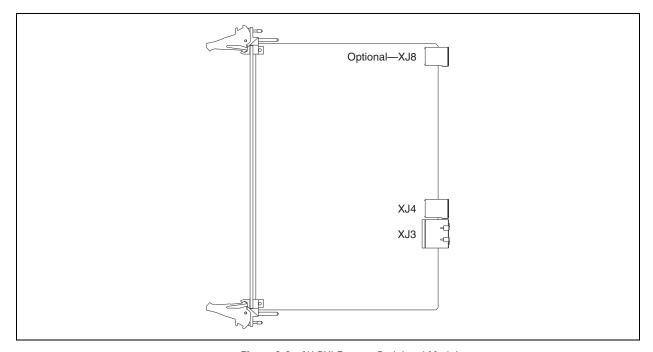

The 3U PXI Express Peripheral Module has two connectors, XJ3 and XJ4. A simplified description of the connector functionality is that XP3/XJ3 are for PCI Express and Differential Triggers and Timing, and XP4/XJ4 is for instrumentation signals that are defined in the PXI-1 specification. The 6U PXI Express Peripheral Module has an Optional eHM connector (required for backplanes), XJ8, that is populated in the upper columns of the legacy J5 location to provide additional power to the 6U Module. The PXI Express specification does not support the use of J3/J4/J5 on 6U Peripheral Modules.

Figures 2-5 and 2-6 show the 3U and 6U PXI Express Peripheral Modules, respectively.

Figure 2-5. 3U PXI Express Peripheral Module

Figure 2-6. 6U PXI Express Peripheral Module

Figures 2-7 and 2-8 show the 3U and 6U PXI Express Peripheral Slots, respectively.

Figure 2-7. 3U PXI Express Peripheral Slot

Figure 2-8. 6U PXI Express Peripheral Slot

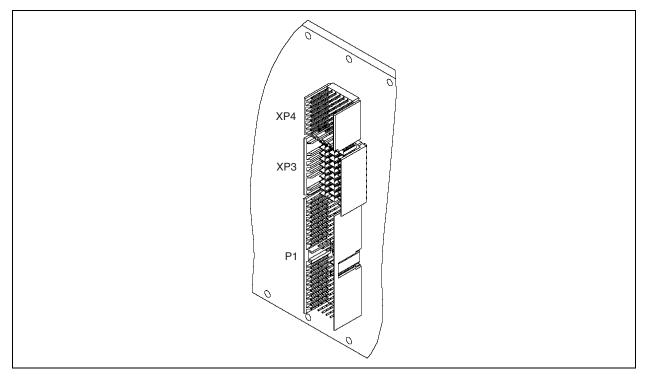

# 2.1.1.3 3U and 6U PXI Express Hybrid Peripheral Slot

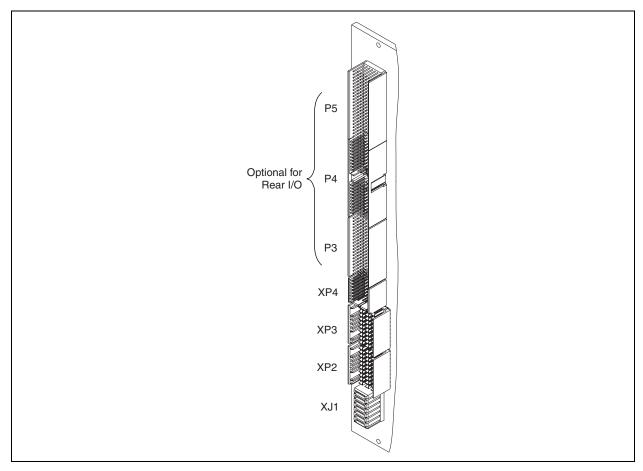

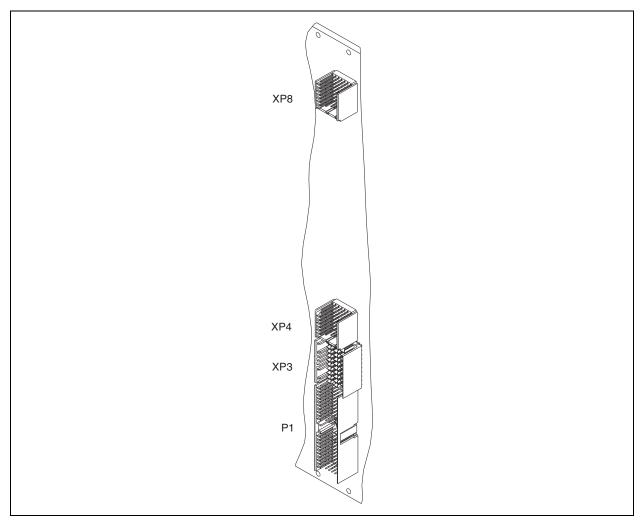

3U Hybrid Peripheral Slots have three connectors: P1, XP3, and XP4. A simplified description of the connector functionality is that P1/J1 are for 32 bit PCI, XP3/XJ3 are for PCI Express and Differential Triggers and Timing, and XP4/XJ4 is for instrumentation signals defined in the PXI-1 specification. 6U Hybrid Peripheral Slots have four connectors: P1, XP3, XP4, and XP8. P3, P4, and P5 are not allowed.

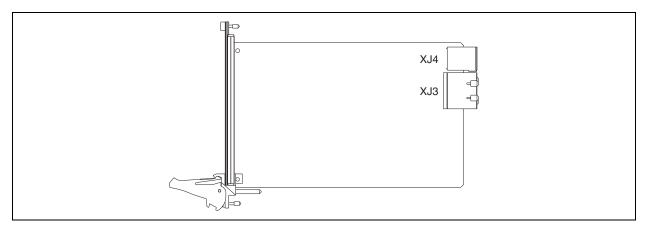

Figures 2-9and 2-10 show the 3U and 6U PXI Express Hybrid Slots, respectively.

Figure 2-9. 3U PXI Express Hybrid Peripheral Slot

Figure 2-10. 6U PXI Express Hybrid Peripheral Slot

# 2.1.1.4 3U and 6U PXI Express System Timing Module and Slot

PXI Express introduces new 3U and 6U Modules called a System Timing Module. It also introduces the associated slots for 3U and 6U called a System Timing Slot.

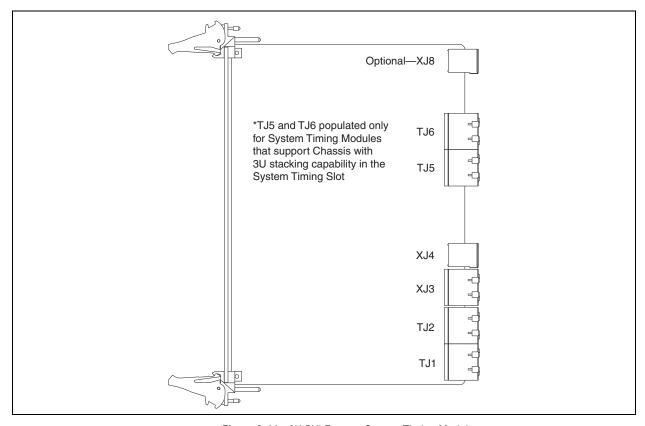

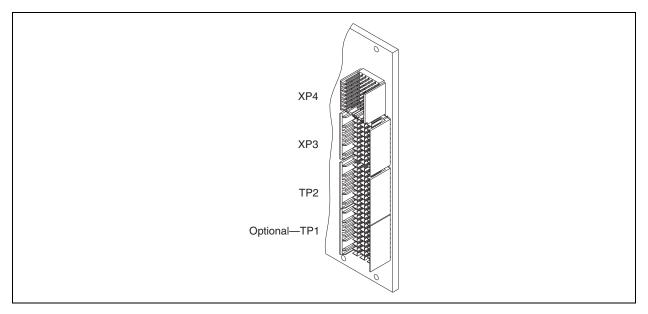

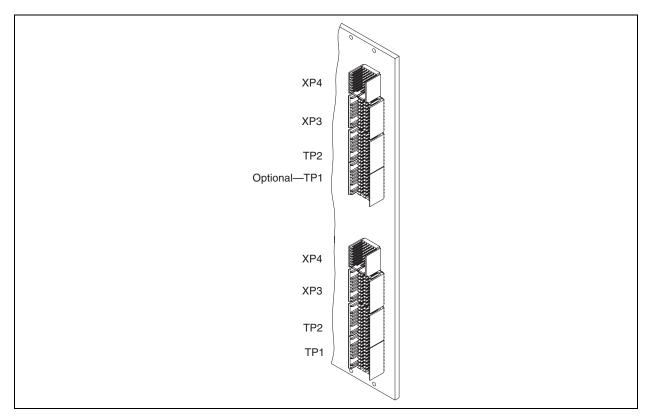

The 3U System Timing Module has four connectors, TJ1, TJ2, XJ3 and XJ4, as shown in Figure 2-11. A simplified description of the connector functionality is TJ1/TP1 and TJ2/TP2 are for fanout of the Differential and Star Triggers, XP3/XJ3 are for PCI Express and Differential Triggers and Timing, and XP4/XJ4 is for instrumentation signals that are defined in the PXI-1 specification.

The 3U Slot has three required connectors: TP2, XP3, and XP4. TP1 is Optional for backplanes that have seven or fewer slots requiring differential triggers.

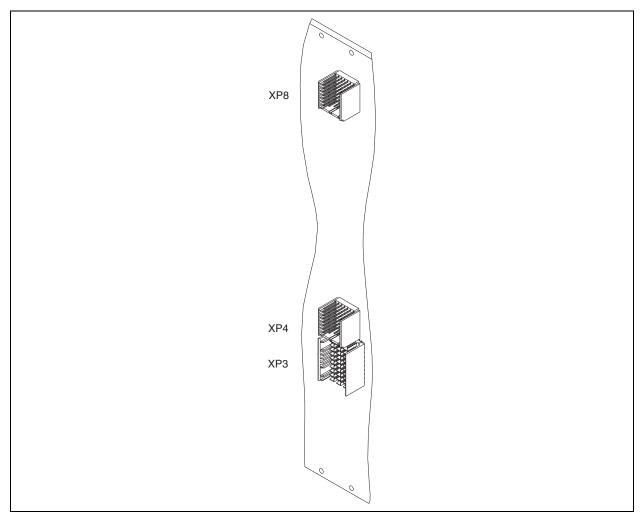

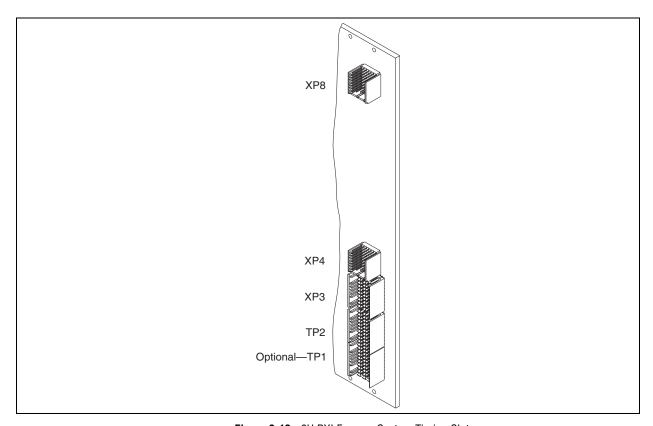

A 6U System Timing Module has the same connectors as the 3U Timing Module, plus the Optional XJ8 connector for additional power.

A 6U System Timing Module designed for 6U Chassis that support stacking 3U Modules with more than 18 Slots has the additional TJ5 and TJ6 connectors. This allows the 6U System Timing Module to connect to additional triggers.

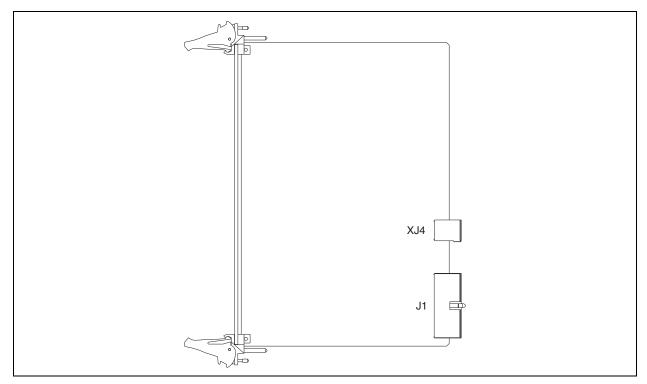

A 6U System Timing Slot that does not allow stacking 3U System Timing Modules has four required connectors: TP2, XP3, XP4, and XP8. TP1 is Optional for backplanes with seven or fewer slots requiring differential triggers.

A 6U System Timing Slot that supports stacking 3U System Timing Modules has seven required connectors: TP1, TP2, XP3, XP4, upper TP2, upper XP3, and upper XP4. The upper TP1 connector is Optional for backplanes with 24 or fewer slots requiring differential triggers.

Figure 2-11. 6U PXI Express System Timing Module

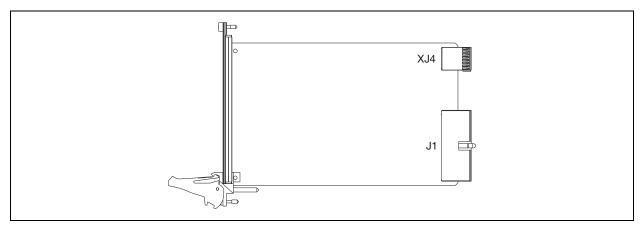

The 3U PXI Express System Timing Slot is shown in Figure 2-12.

Figure 2-12. 3U PXI Express System Timing Slot

The 6U Timing Module Slot is shown in Figures 2-13 and 2-14.

Figure 2-13. 6U PXI Express System Timing Slot

Figure 2-14. 6U PXI Express System Timing Slot with Stacked 3U Support

#### 2.1.1.5 PXI-1 Slot

In a PXI Express Chassis, there may be slots that support PXI boards as they are defined in PXI-1 (*PXI Hardware Specification*, Revision 2.2). These slots meet the mechanical requirements of the *PXI Hardware Specification* and are referred to as PXI-1 slots.

# 2.1.1.6 3U and 6U Hybrid Slot Compatible PXI-1 Peripheral Module

PXI-1 or an associated ECN defines a 3U and 6U Hybrid Slot Compatible PXI-1 Peripheral Module that consists of a 3U or 6U PXI-1 Module where the J2 HM connector has been replaced with an eHM connector. The eHM connector is a modified 2 mm HM connector that includes application keying and is installed in the same location as the upper eight columns of the PXI-1 J2 connector. This board type may be used in any PXI-1 or PXI Express Hybrid Slot. Figures 2-15 and 2-16 show the 3U and 6U Hybrid Slot Compatible PXI-1 Modules.

Figure 2-15. 3U Hybrid Peripheral Slot Compatible PXI-1 Module

Figure 2-16. 6U Hybrid Peripheral Slot Compatible PXI-1 Module

# 2.1.2 System Slot and System Timing Module Location

PXI Express defines the System Slot location to be the furthest left slot within a Chassis and to be numbered Slot 1. This defined arrangement is a subset of the numerous possible configurations allowed by CompactPCI Express (a CompactPCI Express System Slot may be located anywhere on a backplane). Defining a single location for the System Slot simplifies integration and increases the degree of compatibility between PXI Express Controllers and Chassis. Furthermore, the *PXI Express Hardware Specification* requires that, if necessary, the System Module should expand to the left into what are defined as Controller expansion slots. Expanding to the left prevents System Modules from using up valuable Peripheral Slots.

Some PXI Express Chassis may integrate the System Module functionality within the Chassis. In such a system, a System Slot is not required, and Peripheral Slots begin their numbering with 2.

PXI Express defines a System Timing Slot that can accept a PXI Express Peripheral Module or a System Timing Module that can provide individual triggers to all other Peripheral Modules and allow the replacement of the System reference clock. The location of the System Timing Slot is not mandated by the specification, which allows backplane designers to optimize the backplane for cost.

#### 2.1.3 Additional Mechanical Features

In addition to the features defined by the PXI-1 Specification, PXI Express has added additional suggestions for cooling and for the measurement and specification of acoustic noise levels.

#### 2.1.4 Interoperability with CompactPCI Express

Interoperability among PXI Express-compliant products and standard CompactPCI Express products is a very important feature provided by this specification and the CompactPCI Specification. Some PXI Express-compatible systems may require components that do not implement PXI Express-specific features. For example, a user may want to use a standard CompactPCI Express network interface Module in a PXI Express Chassis. Likewise, some users may choose to use a PXI Express-compatible Module in a standard CompactPCI Express Chassis. In these cases, the user cannot use PXI Express-specific Functions, but still can use the basic Module Functions.

Note that interoperability between PXI Express products and other application-specific implementations of CompactPCI Express products (which may define other signal definitions for the I/O pins of the XP4/XJ4 connectors) is not guaranteed. The CompactPCI Express specification provides mechanical keying of the XP4/XJ4 connectors for both PXI Express products and application-specific CompactPCI Express products to prevent electrical conflict between them.

#### 2.1.5 Typical System Components

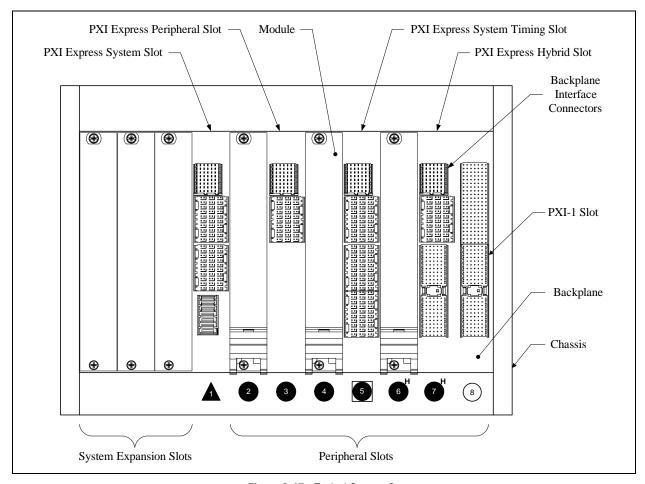

Figure 2-17 presents an example PXI Express system to help illustrate the following key words (in *italics*). A PXI Express System is composed of a *Chassis* that supports the PXI Express *backplane* and provides the means for supporting the System Controller and Peripheral *Modules*. The Chassis may have one *System Slot* and must have one or more *Peripheral Slots*. Any number of *System Expansion Slots* may be available to the left of the System Slot. The *System Timing Slot* may reside in any of the available slots to the right of Slot 1. The backplane carries the *interface connectors* (XP1, XJ2, etc.) and provides the interconnection between the Controller, Peripheral and Timing Slots.

Figure 2-17. Typical System Components

# 2.1.6 Chassis Supporting Stacking 3U Modules in a 6U Slot

Just as with the PXI-1 Specification, PXI Express allows for efficient use of 3U Modules in a 6U Chassis. 6U PXI Express Chassis can support stacking of certain combinations of 3U Modules in a single 6U Slot. This allows one 3U Module to be plugged into the lower position of a 6U Slot, and another 3U Module to be plugged into the upper position of the same 6U Slot simultaneously. This can be accomplished mechanically using a 3U/3U adapter or using commercially available Subrack center extrusions. A 6U PXI Express Chassis may have any number of 6U Slots that support this feature. Figure 2-18 shows a general configuration of a 6U Chassis supporting 3U Module stacking. A 6U PXI Express Chassis may have any number of 6U Slots that support this feature.

Figure 2-18. Example of a PXI Express Chassis that Supports 3U Stacking

X = GLYPH FOR APPROPRIATE SLOT TYPE

# 2.2 Electrical Architecture Overview

In the same way that PXI combined instrumentation features with the desktop computer bus standard of PCI, PXI Express combines instrumentation features with the new desktop computer bus standard of PCI Express. The instrumentation features of PXI Express include many of the PXI instrumentation features, as well as a new differential 100 MHz system clock, new point-to-point differential triggers, and a new point-to-point variable frequency clock. These features are implemented on the backplane for the highest performance instrumentation timing and synchronization.

System Controller Slot

#### 2.2.1 Features Leveraged from CompactPCI Express

PCI Express is one of the main features that PXI Express leverages from CompactPCI Express. PXI Express Systems can have up to 24 GBytes/sec per direction of data moving to and from the System Module, and an individual PXI Express Peripheral Module can have up to 8GBytes/sec per direction. Considering that PCI Express Switches have the ability for multiple separate data paths to be transferring data between PCI Express devices at the same time, the possibility exists for data rates upto 128 GBytes/sec per direction within a PXI Express System. The amount of bandwidth for a system is implementation specific and allows PXI Express suppliers to develop systems that meet their customers' needs in terms of cost and performance.

Electrical rules that are leveraged from the CompactPCI Express specification into PXI Express include but are not limited to the following:

- PCI Express transmit and receive electrical signaling definitions and budgets

- PCI Express reference clock

- PCI Express sideband signals

- SMBus

- Backplane identification and capability via SMBus

- Signals used for power supply control

- Power supply requirements

- Module and slot pin assignments with the exception of the additional instrumentation signals

- PCI with certain slot types

Table 2-2 shows the components that are interoperable between the two specifications. Note that when PXI Express Modules are used in CompactPCI Express Chassis, the PXI Express Module's instrumentation features are not usable.

Table 2-2. PXI and PXI Express Module Interoperability

|                                                    | CompactPCI Express Component |                 |                              |                               |                |                |                                   |

|----------------------------------------------------|------------------------------|-----------------|------------------------------|-------------------------------|----------------|----------------|-----------------------------------|

| PXI Express Component                              | System<br>Slot               | System<br>Board | Type 2<br>Peripheral<br>Slot | Type 2<br>Peripheral<br>Board | Hybrid<br>Slot | Legacy<br>Slot | CompactPCI<br>Peripheral<br>Board |

| PXI Express System Slot                            |                              | OK              |                              |                               |                |                |                                   |

| PXI Express System Module                          | ОК                           |                 |                              |                               |                |                |                                   |

| PXI Express Peripheral Slot                        |                              |                 |                              | OK                            |                |                |                                   |

| PXI Express Peripheral Module                      |                              |                 | OK                           |                               | OK             |                |                                   |

| PXI Express Hybrid Slot                            |                              |                 |                              | OK                            |                |                | OK <sup>1</sup>                   |

| Hybrid Slot Compatible PXI-1 Module                |                              |                 |                              |                               | OK             | ОК             |                                   |

| System Timing Slot                                 |                              |                 |                              | OK                            |                |                |                                   |

| System Timing Module                               |                              |                 | ОК                           |                               |                |                |                                   |

| PXI-1 Slot                                         |                              |                 |                              |                               |                |                | OK                                |

| PXI-1 Module                                       |                              |                 |                              |                               |                | OK             |                                   |

| <sup>1</sup> CompactPCI Peripheral Board will work | if it has J1 only            | <u>l</u><br>y.  |                              |                               |                | OK.            | 1                                 |

#### 2.2.2 Features Leveraged from the PXI Hardware Specification

PXI Express products can take advantage of the increase in data performance while implementing the instrumentation features in the PXI-1 Specification. Each PXI Express Module and slot type defined in this specification can leverage the PXI 10 MHz system clock (PXI\_CLK10), the PXI-bused trigger lines, a Local Bus line, and PXI star trigger as defined in the PXI-1 Specification, in addition to the new instrumentation features defined in this specification. PXI-1 slots implemented in PXI Express systems also maintain the PXI Local Bus. PXI Express slots have the potential for a virtual local bus by taking advantage of PCI Express Switches allowing multiple data paths to transfer data between PCI Express devices at the same time. Determinism of data movement with such a virtual local bus may be PCI Express Switch and data dependent.

#### 2.2.3 New Instrumentation Features

The system timing and synchronization capabilities of PXI are a key differentiation from other instrumentation form factors. PXI was created by adding those features to the high-bandwidth PCI bus and compact modular form factor of CompactPCI while maintaining reasonable implementation cost. The timing and triggering capabilities of PXI are retained in this specification and will continue to solve many system applications in PXI. With the advances in technology affording higher performance, low-cost differential signaling, and the differential connectors necessary for PCI Express already required, PXI Express builds on the existing capabilities by providing a differential system clock, differential synchronization, and differential star trigger and clock signals from a new System Timing Module. The key advantages of providing differential clocking and synchronization is the increased noise immunity provided to instrumentation clocks and the ability to transmit higher frequency clocks. These high-frequency clocks not only allow for higher performance, but also match well with modern processes and allow for low-cost products to remove clock multiplication circuits in many cases. The new features are added in a way to be compatible and highly interoperable with existing PXI Modules. The following sections will describe the new additions. Figure 2-19 shows one example of how the instrumentation signals are implemented on a PXI Express backplane that has a System Timing Slot.

Figure 2-19. Instrumentation Signal Implementation Example

Figure 2-20 shows how the instrumentation signals are mapped to the connectors of the Hybrid Slot, PXI Express Peripheral Slot, and the System Timing Slot.

Figure 2-20. Instrumentation Signals Connector Mapping

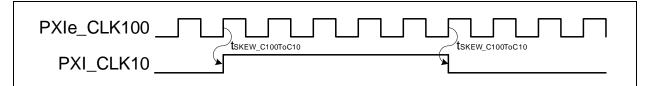

#### 2.2.3.1 High-Frequency System Reference Clock

The High-Frequency System Reference Clock, or PXIe CLK100 as it is called out in the specification, is the most significant addition for timing in PXI Express. This signal provides a differential, 100 MHz LVPECL clock to each PXI Express Peripheral Slot in the system. Advancing technology has allowed PXI to adopt differential clocking, which provides for increased noise immunity in the backplane. This allows instrumentation Modules to receive a clock with low jitter and improve overall system performance. The differential technology also allows for a higher frequency reference clock of 100 MHz. This not only allows for higher performance clocking, but also allows the cost of Modules to be lowered by eliminating clock multiplication for Modules able to work with PXIe CLK100 and divisions directly. The PXIe CLK100 is added into the specification in a way to be completely interoperable with PXI CLK10. The PXI CLK10 and PXIe\_CLK100 are phase aligned and allow for highly accurate synchronization of devices, including all PXI-1 compliant devices, no matter which clock is used.

# 2.2.3.2 Differential Synchronization Signal

With the High-Frequency System Reference Clock (PXIe\_CLK100) comes the need to accurately synchronize Modules using this reference clock along with those using PXI\_CLK10. The Differential Synchronization Signal or PXIe SYNC100 is routed by the backplane to each Module and provides this capability. This signal is synchronous to PXIe\_CLK100 and asserts one out of every 10 clocks to indicate the phase relationship of the 10 MHz and 100 MHz reference clocks. This is key for synchronization and triggering in that it allows the existing triggering capabilities to be used and interoperate. Devices using the Trigger Bus can send triggers synchronous to PXI\_CLK10 no matter what system reference clock is used. The PXIe\_SYNC100 also provides a synchronization signal for Modules wanting to divide the 100 MHz reference clock for use on the Module. This allows multiple Modules to begin the clock division on the same clock edge without requiring a high-frequency trigger bus.

### 2.2.3.3 Differential Triggers

Previous PXI specifications could take advantage of the low cost of TTL logic to provide a complete timing and synchronization system. While TTL logic provided efficient implementations, it does come with a limit on the frequencies that may be transmitted in the system. With PXI Express, the clocking and triggering system can take advantage of the lowered cost of differential signaling and provide high-quality and high-frequency connections to each Module. In the same way that PXI\_STAR allows a direct connection between each Module to a central timing resource, the Differential Star Triggers allows for three direct, high-frequency connections back to the System Timing Module. A key benefit of these signals is the ability to transmit high-frequency, high-quality clocks to and from Modules in a PXI system. By having multiple connections, a larger number of system applications may be solved by providing increased routing capabilities. While a primary application of PXIe\_DSTAR will be clock distribution, the signals are flexible and allow for a large number of unique applications of these connections.

### 2.2.3.4 System Timing Module

The Slot 2 or Star Trigger Slot of PXI-1 provides access to advanced system timing applications with individual connections to each Module and the ability to replace the system clock reference. With the addition of the Differential Star Triggers and High-Frequency System Reference Clock, a larger number of high-performance connections are required to be provided by the backplane to the Modules. The System Timing Module (STM) is the connection point for the three starred signals added to each Module. The STM becomes the central connection point and routing manager for the most advanced timing and synchronization capabilities for a PXI Express system. The System Timing Module in PXI Express Systems replaces the Star Trigger Module defined in PXI-1 while it retains the connection point for PXI\_STAR to each Module and it provides the connection point for clock replacement in the backplane. The STM is also key in providing the access to support highly synchronized systems across multiple Chassis of heterogeneous systems. While backplanes will provide the capability to support an STM, the System Timing Slot (STS) may accept a PXI Express Peripheral Module if the advanced timing synchronization capabilities are not necessary in a system.

#### 2.2.4 Slot Identification

PXI Express has explicit hardware support for geographical addressing. A PXI Express device can determine its slot number by reading the GA(4:0) pins. Previously, to create the pxisys.ini file describing the topology of the PXI system, a PXI resource manager needed to use the run time PCI device tree, the chassis.ini files, and vendor-specific information about the PCI topology of the Slot 1 Controller. Using the new hardware support, a full PCI bus tree is no longer needed. Each Module can discover its slot number independently.

#### 2.2.4.1 Module Drivers and the GA Pins

For instrument drivers, VISA implementations, and application software to find a particular device by slot number, the driver for each Module must provide a mechanism to report its slot number to other software components in the system. This mechanism is defined in the PXI-6: PXI Express Software Specification.

# 2.2.4.2 Determining the Chassis Number

Although there is explicit hardware support for determining a Module's slot number, the mechanism for determining a Chassis number requires knowledge of the bus and device numbers of some of the PCI Express Switches and of the Modules in the system. The PXI Express Software specification describes the interfaces for discovering the Chassis number for a PXI Express Module.

#### 2.2.5 Controller Identification

PXI Express has hardware support for identification of a PXI Express Chassis using an EEPROM on the SMBus. PXI Express also uses information about the bus numbers of the links from the system Module to the Chassis to enumerate which devices are in which Chassis. Therefore, the *PXI Express Software Specification* defines a mechanism for identifying what Controllers exist, how those Controllers access the SMBus, and what bus numbers are subordinate to that Controller.

The *PXI Express Software Specification* specifies an interface for accessing the SMBus using a Slot 1 Controller. There is a one-to-one correspondence between Slot 1 Controllers and instances of the PXI Express SMBus Controller interface.

#### 2.2.6 Chassis Identification

PXI Express leverages the requirements set in the CompactPCI Express specification for the Backplane Identification and Capability EPROM. This EPROM is accessed by the system Module via the SMBus and gives the PXI Express system a way to uniquely identify the vendor, model, revision, and serial number of the Chassis. It also provides information on the slots within the Chassis and the PCI Express topology. This information can be used by software to load a Chassis driver to provide additional information about the Chassis or access backplane and Chassis functionality.

### 2.2.7 Power Requirements

The power requirements for PXI Express systems include the following defined in CompactPCI Express:

- Power rails

- Regulation

- Ripple and noise

- Decoupling

- Power rail timing

- Power supply signals to and from the system Module

PXI Express additionally includes Chassis power supply minimum current requirements per voltage rail for each slot type. This guarantees a high level of interoperability between Modules and Chassis and gives guidance to PXI Express Module designers on how much current they can expect from a Chassis. Power requirements for PXI-1 slots implemented in PXI Express systems are defined in the PXI-1 Specification.

# 2.3 Software Architecture Overview

PXI Express introduces new software features for managing the new hardware features of CompactPCI Express and PXI Express. These new features include:

- A software interface for accessing SMBus devices, such as the serial EEPROM of each Chassis.

- A software interface for accessing the slot number of each Module as provided by the GA pins.

- A mechanism for associating a Chassis number with the Modules in each Chassis.

- A software protocol for enumerating PXI components, such as Controllers, Modules, Chassis, and other resources.

- A namespace for those PXI components.

- A general registration mechanism for services implemented by the drivers for PXI components.

- Standard software interfaces for services implemented by Controllers, Chassis and Modules.

The PXI Express Software Specification requires each Controller, Chassis, and Module to include software implementing certain services, and to register those services. By creating standards for these services and how

they are registered, the *PXI Express Software Specification* provides a new level of interoperability. If, for example, a Controller, a Chassis, a Module, and a VISA implementation are each provided by a different vendor, all of the following are possible:

- The VISA implementation can determine the physical location of the Module by interacting with the Module driver.

- The Chassis driver can control backplane resources by using the SMBus driver on the Slot 1 Controller.

- A configuration tool can determine the list of Chassis and Modules in the system.

The new software requirements and features for PXI Express are specified in the PXI Express Software Specification.

This Page Intentionally Left Blank

# 3. Mechanical Requirements

This section defines the mechanical requirements for PXI Express systems. It discusses the maximum number of slots, the location of the system slot, slot numbering, PXI-1 slots, Chassis requirements, connector requirements, Module types, the interoperability of the Controller with the Chassis, the PXI Express logo/glyphs, environmental testing, and cooling.

# 3.1 Drawing Standard

The drawings in this specification shall be interpreted per ANSI Y14.100.

# 3.2 Dimensional Units

Dimensions in this specification are in millimeters unless otherwise specified.

# 3.3 Chassis Subrack Mechanical Requirements

**RULE:** Just as with PXI-1, CompactPCI, and CompactPCI Express, a PXI Express Chassis SHALL use PICMG 2.0-compliant Chassis Subracks.

# 3.4 Minimum Slot Requirements to be a PXI Express Chassis

**RULE:** A PXI Express Chassis SHALL at least have either one PXI Express Peripheral Slot or one Hybrid Slot.

RULE: A PXI Express Chassis SHALL NOT have a Star Trigger Slot as defined in the PXI-1 Specification.

**RECOMMENDATION:** A PXI Express Chassis SHOULD have a System Timing Slot.

# 3.5 Features Leveraged from PXI-1: PXI Hardware Specification

#### 3.5.1 Maximum Number of Slots

Since the CompactPCI Express specification accommodates 31 slots based on the definition of the Geographical Addressing pins, it is necessary to limit a PXI Express Chassis to 31 slots.

RULE: A PXI Express Chassis SHALL NOT have more than 31 slots.

### 3.5.2 System Slot Location and Rules

All PXI Express-compatible systems require a backplane/Chassis, a System Timing Slot, and at least either one PXI Express Peripheral Slot or one Hybrid Slot. A System Slot is not a requirement if the system Module functionality is built into the Chassis. If the Chassis does have a System Slot, it allows users to mix and match different Controllers. However, because the CompactPCI Express specification allows a System Slot to be located anywhere relative to Peripheral Slots, the possibility for confusion and incompatibility exists. To address this problem the following rules must be followed for PXI Express-compatible systems:

**RULE:** The System Slot SHALL be defined as the leftmost PXI slot in a PXI Chassis/backplane. For documentation purposes, this slot is counted as one *System* Slot.

**RECOMMENDATION:** If the System Module requires more than one slot width, it SHOULD extend to the LEFT of the System Slot in full slot increments (one slot equals 20.32 mm, or 0.8 in.) into additional Controller expansion slots.

OBSERVATION: In a PXI Express system, these additional Controller slots are for physical expansion of the System Controller Module only and cannot support Peripheral Modules. These slots DO NOT have connectors that interface to PCI Express links routed on the backplane.

**OBSERVATION:** Extending the System Module to the LEFT allows all PXI Express Peripheral Slots to be used.

**RECOMMENDATION:** The System Module SHOULD NOT extend to the RIGHT of the System Slot into Peripheral Slots.

**OBSERVATION:** If a System Module expands to the right, the number of usable PXI Express Peripheral Slots may be compromised.

RULE: Every PXI Express System Module SHALL clearly document how many Controller expansion slots (to the left of the System Slot) and Peripheral Slots it occupies.

RULE: Every PXI Express Chassis SHALL clearly document how many Peripheral and Controller Expansion Slots are available.

**OBSERVATION:** The two preceding rules help ensure that end users can easily determine whether a particular Controller-Chassis pair is compatible and how many Peripheral Slots are available.

Figure 2-17 depicts typical System Expansion Slot designations in a PXI Express System.

#### 3.5.3 Slot Numbering and Orientation

PXI Express Chassis slot numbering is handled the same way that the PXI-1 Specification requires. The exception is that PXI Express allows for Chassis that have the System Module to be built in.

RULE: PXI Express Chassis with a System Slot SHALL meet the slot numbering requirements set in the PXI-1 Specification.

RULE: PXI Express Chassis without a System Slot (the System Module is built in), SHALL meet the slot numbering requirements set in the PXI-1 Specification, except the slots will have their numbering begin at the number 2.

PERMISSION: Slot orientation and numbering schemes other than those defined in PXI-1 MAY be used as long as it is clear and logical for the end user.

#### 3.5.4 PXI-1 Slot

In a PXI Express Chassis, there may be slots that support PXI boards as they are defined in PXI-1 (PXI Hardware Specification, Revision 2.2). These slots meet the mechanical requirements of the PXI Hardware Specification and are referred to as PXI-1 slots.

**PERMISSION:** PXI-1 3U and 6U Peripheral Modules and Slots are MAY be used in PXI Express Systems.

RULE: PXI-1 slots in a PXI Express Chassis SHALL meet the mechanical requirements set in the PXI-1 Specification.

RULE: PXI-1 Peripheral Modules SHALL NOT be plugged into Hybrid Peripheral Slots unless they meet the requirements for Hybrid Slot Compatible PXI-1 Modules as defined by this specification.

RECOMMENDATION: PXI-1 3U and 6U Peripheral Modules SHOULD also meet the side-2 component height recommendation as defined by the CompactPCI Express specification to minimize mechanical interference issues.

### 3.5.5 Hybrid Slot-Compatible PXI-1 Peripheral Modules

PXI-1 or an associated ECN defines a 3U and 6U Hybrid Slot Compatible PXI-1 Peripheral Module that consists of a 3U or 6U PXI-1 Module where the J2 HM connector has been replaced with an eHM connector. The eHM connector is a modified 2 mm HM connector that includes application keying and is installed in the same location as the upper eight columns of the PXI-1 J2 connector. This board type may be used in any PXI-1 or PXI Express Hybrid Slot.

**OBSERVATION:** A Hybrid Slot Compatible PXI-1 Peripheral Module MAY be used in a legacy PXI-1 or PXI Express Hybrid Slot.

# 3.6 Features Leveraged from CompactPCI Express Specification

Just as PXI-1 was based on CompactPCI, PXI Express is based on CompactPCI Express, which has integrated PCI Express into a CompactPCI type architecture. This section outlines the features rules, suggestions, permissions, and observations leveraged from that specification.

**RULE:** All mechanical requirements defined by the CompactPCI Express specification SHALL be met unless stated otherwise in this specification.

#### 3.6.1 Module Connector Requirements

#### 3.6.1.1 Advanced Differential Fabric (ADF) Connector

**RULE:** PXI Express Modules SHALL use the ADF-F-3-10-2-F-25 connector as defined by the CompactPCI Express specification.

### 3.6.1.2 Enriched Hard-Metric (eHM) Connector

**RULE:** PXI Express Modules SHALL use the eHM-F2 connector as defined by the CompactPCI Express specification.

# 3.6.1.3 Universal Power (UPM) Connector

**RULE:** System Controller Modules SHALL use the UPM-M-7 or UPM-M-7-HP connector as defined by the CompactPCI Express specification.

### 3.6.2 Backplane Connector Requirements

# 3.6.2.1 Advanced Differential Fabric (ADF) Connector

**RULE:** PXI Express Slots SHALL use the ADF-M-3-10-2-B-25 or ADF-M-3-10-2-S-25-0100 connector as defined by the CompactPCI Express specification.

# 3.6.2.2 Enriched Hard-Metric (eHM) Connector

**RULE:** PXI Express Slots SHALL use the eHM-M2-HP or eHM-M2 connector as defined by the CompactPCI Express specification.

# 3.6.2.3 Universal Power (UPM) Connector

**RULE:** System Controller Slots SHALL use the UPM-F-7 connector as defined by the CompactPCI Express specification.

### 3.6.3 3U and 6U Module Requirements

#### 3.6.3.1 System Module

**RULE:** 3U and 6U PXI Express Modules SHALL meet the mechanical requirements as defined in the CompactPCI Express specification.

**OBSERVATION:** 6U PXI Express System Modules and backplanes MAY use J3/P3, J4/P4, and J5/P5 if desired for rear I/O applications.

### 3.6.3.2 PXI Express Peripheral Module

**RULE:** The 3U PXI Express Peripheral Modules SHALL meet the mechanical requirements for the 3U Type 2 Peripheral Module as defined in the CompactPCI Express specification.

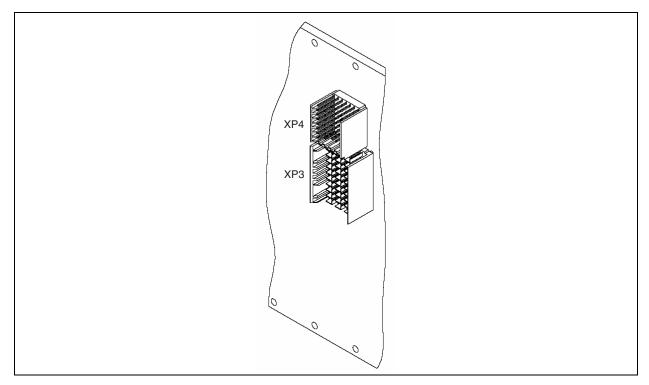

**RULE:** The 6U PXI Express Peripheral Modules SHALL meet the mechanical requirements for 6U Type 2 Peripheral Boards as defined in the CompactPCI Express specification with the exception that the J3/J4/J5 connectors SHALL NOT be used. The 6U PXI Express Peripheral Module PCB SHALL meet the requirements defined by Figure 3-1.

**RULE:** 6U PXI Express Peripheral Modules that are not 6U System Timing Modules SHALL NOT have any connectors other than the XJ3, XJ4, and XJ8 connectors.

**PERMISSION:** 6U PXI Express Peripheral Modules MAY populate the Optional eHM connector, in the XJ8 position as shown in Figure 3-1, when additional power is required.

Figure 3-1. 6U PXI Express Peripheral Module PCB

Figure 3-2. 6U PXI Express Peripheral Module

### 3.6.4 Backplane Requirements

**RULE:** 3U and 6U PXI Express backplanes SHALL meet the size, mechanical mounting hole, and tolerance requirements as defined in the CompactPCI Express specification.

Requirements for the various connector locations are defined in further detail in the following sections.

# **3.6.4.1 System Slot**