# **PXI**\*-2

# PXI Software Specification

PCI eXtensions for Instrumentation

An Implementation of *CompactPCI*™

Revision 2.6 March 20, 2020

#### IMPORTANT INFORMATION

#### Copyright

© Copyright 2003–2020 PXI Systems Alliance. All rights reserved.

This document is copyrighted by the PXI Systems Alliance. Permission is granted to reproduce and distribute this document in its entirety and without modification.

#### NOTICE

The *PXI Software Specification* is authored and copyrighted by the PXI Systems Alliance. The intent of the PXI Systems Alliance is for the *PXI Software Specification* to be an open industry standard supported by a wide variety of vendors and products. Vendors and users who are interested in developing PXI-compatible products or services, as well as parties who are interested in working with the PXI Systems Alliance to further promote PXI as an open industry standard, are invited to contact the PXI Systems Alliance for further information.

The PXI Systems Alliance wants to receive your comments on this specification. Visit the PXI Systems Alliance web site at http://www.pxisa.org/ for contact information and to learn more about the PXI Systems Alliance.

The attention of adopters is directed to the possibility that compliance with or adoption of the PXI Systems Alliance specifications may require use of an invention covered by patent rights. The PXI Systems Alliance shall not be responsible for identifying patents for which a license may be required by any PXI Systems Alliance specification, or for conducting legal inquiries into the legal validity or scope of those patents that are brought to its attention. PXI Systems Alliance specifications are prospective and advisory only. Prospective users are responsible for protecting themselves against liability for infringement of patents.

The information contained in this document is subject to change without notice. The material in this document details a PXI Systems Alliance specification in accordance with the license and notices set forth on this page. This document does not represent a commitment to implement any portion of this specification in any company's products.

The PXI Systems Alliance makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The PXI Systems Alliance shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Compliance with this specification does not absolve manufacturers of PXI equipment from the requirements of safety and regulatory agencies (UL, CSA, FCC, IEC, etc.).

#### **Trademarks**

PXI<sup>TM</sup> is a trademarks of the PXI Systems Alliance.

PICMG<sup>TM</sup> and CompactPCI® are trademarks of the PCI Industrial Computation Manufacturers Group.

Product and company names are trademarks or trade names of their respective companies.

# **PXI Software Specification Revision History**

This section is an overview of the revision history of the PXI Software Specification.

#### Revision 2.1, February 4, 2003

This is the first public revision of the PXI specification.

#### Revision 2.2, September 8, 2003

Added specification number and updated relevant documents list.

#### Revision 2.3, January 22, 2008

Added 64-bit Windows system framework. Adjusted references to VISA specifications. Corrected several errata.

#### **Revision 2.4, October 18, 2012**

Added new chassis ini file content related to the PXI Trigger Manager specified in PXI-9.

Added description of registration and selection mechanism for Resource Manager.

Modified description of Resource Manager algorithm to include assignment of Trigger Managers per chassis.

Added requirements for chassis description file names and the chassis description file path.

#### **Revision 2.5, May 31, 2018**

Added support for the Linux operating system.

Updated rules for proper values of tag lines on the slot 1 Slot Descriptor.

Clarified intended handling of slot 1 Star Trigger lines for PXI Express chassis.

Added additional text on proper handling of file locks.

#### **Revision 2.6, March 20, 2020**

Updated PCISlotPath and PCISlotPathRootBus values for Slot 1 in example System Description File.

Added text to recommend specific timestamp checking mechanisms in Windows frameworks.

This Page Intentionally Left Blank

# **Contents**

| 1. | Introduc | tion         |              |                                                |    |

|----|----------|--------------|--------------|------------------------------------------------|----|

|    | 1.1      | Objectives   | J            |                                                | 1  |

|    | 1.2      | -            |              | d Scope                                        |    |

|    | 1.3      | Backgrour    | nd and Term  | ninology                                       | 1  |

|    | 1.4      | Applicable   | Document     | is                                             | 2  |

| 0  | Handma   | ua Dagaulini | lian Filan   |                                                |    |

| ۷. |          | re Descrip   |              |                                                |    |

|    | 2.1      |              |              |                                                |    |

|    | 2.2      |              | -            | ements                                         |    |

|    |          |              |              | scriptor                                       |    |

|    | 2.2      |              |              | Compatibility with Previous PXI Specifications |    |

|    | 2.3      |              |              | iles                                           |    |

|    |          |              | •            | cription Definitions                           |    |

|    |          |              |              | lanager Descriptor                             |    |

|    |          |              |              | criptor                                        |    |

|    |          |              |              | griptorgment Descriptor                        |    |

|    |          |              | •            | Descriptor                                     |    |

|    |          |              |              | lge Descriptor                                 |    |

|    |          |              |              | ng Specification Descriptor                    |    |

|    |          |              |              | · Descriptor                                   |    |

|    |          |              |              | otor                                           |    |

|    |          |              | 2.3.10.1     | PCI Slot Path                                  |    |

|    |          | _            | 2.3.10.2     | Local Bus Routings                             |    |

|    |          | 2.3.11       | System Des   | cription File Example                          |    |

|    | 2.4      |              | •            | ïles                                           |    |

|    |          |              |              | scription Definitions                          |    |

|    |          |              |              | scriptor                                       |    |

|    |          |              |              | gment Descriptor                               |    |

|    |          |              | 2.4.3.1      | System Controller Module Slot Considerations   |    |

|    |          | 2.4.4        | Гrigger Bus  | Descriptor                                     | 30 |

|    |          | 2.4.5        | Гrigger Brid | dge Descriptor                                 | 30 |

|    |          | 2.4.6 I      | Line Mappi   | ng Spec Descriptor                             | 32 |

|    |          |              |              | Descriptor                                     |    |

|    |          |              | -            | criptor                                        |    |

|    |          |              |              | otor                                           |    |

|    |          |              |              | scription File Examples                        |    |

|    |          |              | 2.4.10.1     | Example 8-Slot PXI Chassis                     |    |

|    |          | 7            | 2.4.10.2     | Example 18-Slot PXI Chassis                    | 37 |

| 3. | Softwar  | e Framewo    | orks and F   | Requirements                                   |    |

|    | 3.1      |              |              | •                                              | 43 |

|    | 3.2      |              |              |                                                |    |

|    | 3.3      |              |              | 1                                              | -  |

|    | 3.4      |              |              | em Framework                                   |    |

|    |          |              |              | 1                                              |    |

|    |          |              |              | f the Framework                                |    |

|    |          |              |              | Requirements                                   |    |

|    |          |              |              | eral Module Requirements                       |    |

|    |          |              | _            | matting                                        |    |

|    |          |              |              | ile Access                                     |    |

|    | 3.5      | 64-bit Win   | idows Syste  | em Framework                                   | 46 |

|    |          | 3.5.1        | ntroduction  | 1                                              | 46 |

|      |           | 3.5.2  | Overview of the Framework                                          | 46             |

|------|-----------|--------|--------------------------------------------------------------------|----------------|

|      |           | 3.5.3  | Controller Requirements                                            | 46             |

|      |           | 3.5.4  | PXI Peripheral Module Requirements                                 | 47             |

|      |           | 3.5.5  | INI File Formatting                                                | 47             |

|      |           | 3.5.6  | Exclusive File Access                                              | 47             |

|      | 3.6       | 32-bit | Linux System Framework                                             | 47             |

|      |           | 3.6.1  | Introduction                                                       | 47             |

|      |           | 3.6.2  | Overview of the Framework                                          | 47             |

|      |           | 3.6.3  | Controller Requirements                                            |                |

|      |           | 3.6.4  | PXI Peripheral Module Requirements                                 | 48             |

|      |           | 3.6.5  | INI File Formatting                                                | 48             |

|      |           | 3.6.6  | Exclusive File Access                                              | 48             |

|      |           | 3.6.7  | Security of PXI Files and Interfaces                               | 49             |

|      | 3.7       | 64-bit | Linux System Framework                                             | 52             |

|      |           | 3.7.1  | Introduction                                                       |                |

|      |           | 3.7.2  | Overview of the Framework                                          | 52             |

|      |           | 3.7.3  | Controller Requirements                                            |                |

|      |           | 3.7.4  | PXI Peripheral Module Requirements                                 | 52             |

|      |           | 3.7.5  | INI File Formatting                                                |                |

|      |           | 3.7.6  | Security of PXI Files and Interfaces                               | 52             |

|      | 3.8       | Suppo  | ort for Existing Instrumentation Standards                         | 53             |

|      |           |        |                                                                    |                |

| 4. 8 | Service F | Regist | ration and Configuration                                           |                |

|      | 4.1       | Overv  | iew                                                                | 55             |

|      | 4.2       | Resou  | rce Manager Registration                                           | 55             |

|      | 4.3       | Syster | n Configuration File Requirements                                  | 5 <del>6</del> |

|      |           | 4.3.1  | Resource Manager Descriptor                                        | 57             |

|      |           | 4.3.2  | Trigger Manager Descriptor                                         | 60             |

|      |           |        |                                                                    |                |

| Tabl | es        |        |                                                                    |                |

|      | Table     | 2-1.   | Version Information Tag Line Descriptions                          | 5              |

|      | Table     | 2-2.   | Version Information Tag Line Descriptions                          | 7              |

|      | Table     | 2-3.   | System Description File – System Tag Line Descriptions             | 8              |

|      | Table     | 2-4.   | System Description File – Chassis Tag Line Description             | 9              |

|      | Table     | 2-5.   | System Description File – PCI Bus Segment Tag Line Descriptions    | 11             |

|      | Table     | 2-6.   | System Description File - Trigger Bus Tag Line Descriptions        | 12             |

|      | Table     | 2-7.   | System Description File – Trigger Bridge Descriptions              | 13             |

|      | Table     | 2-8.   | System Description File – Line Mapping Spec Descriptions           | 14             |

|      | Table     | 2-9.   | System Description File – Star Trigger Tag Line Descriptions       | 15             |

|      | Table     | 2-10.  | System Description File – Slot Tag Line Descriptions               | 16             |

|      | Table     | 2-11.  | Chassis Description File – Chassis Tag Line Descriptions           | 27             |

|      | Table     | 2-12.  | Chassis Description File – PCI Bus Segment Tag Line Descriptions   | 28             |

|      | Table     | 2-13.  | Chassis Description File – Trigger Bus Tag Line Descriptions       | 30             |

|      | Table     | 2-14.  | Chassis Description File – Trigger Bridge Descriptions             | 30             |

|      | Table     | 2-15.  | Chassis Description File – Line Mapping Spec Descriptions          |                |

|      | Table     |        | Chassis Description File – Star Trigger Tag Line Descriptions      |                |

|      | Table     |        | Chassis Description File – Bridge Tag Line Descriptions            |                |

|      | Table     | 2-18.  | Chassis Description File – Slot Tag Line Descriptions              |                |

|      | Table     | 3-1.   | Development Environments Supported by PXI Modules Under Windows    |                |

|      | Table     | 3-2.   | Development Environments Supported by PXI Modules Under Linux      |                |

|      | Table     |        | System Configuration File – Resource Manager Tag Line Descriptions |                |

|      | Table     | 4-2.   | System Configuration File—Trigger Manager Tag Line Descriptions    | 60             |

# 1. Introduction

This section explains the objectives and scope of the PXI Software Specification. It also describes the intended audience and lists relevant terminology and documents. Note that this specification is intended to supplement the PXI Hardware Specification. Refer to the PXI Hardware Specification for general background on PXI and its electrical and mechanical requirements.

# 1.1 Objectives

The PXI software architecture, in addition to PXI's mechanical and electrical requirements, is a key component in furthering the standard's interoperability and ease of integration goals. The PXI Software Specification was created to supplement the PXI Hardware Specification in clarifying and addressing common software requirements in PXI systems. The software specification's purposes are to describe the capabilities of PXI hardware components using standard hardware description files and to promote interoperability among PXI vendors with respect to software requirements. The software specification addresses a variety of issues, including hardware description, hardware resource management, operating system framework definition, and the incorporation of existing instrumentation software standards.

The primary objective of the *PXI Software Specification* is to define a set of hardware description files for characterizing PXI components and their capabilities. Using standard file formats, device drivers, configuration software, and systems integrators can implement ease-of-use features such as geographic slot identification and chassis identification. These hardware description files can also serve as a repository for managing PXI hardware resources, including the PXI trigger bus, the PXI star trigger, and the PXI local bus.

A secondary objective of the *PXI Software Specification* is to define standard operating system frameworks and to incorporate existing instrumentation software standards. Additional software requirements include the support of standard operating system frameworks such as Microsoft Windows and Linux, and the support of the VISA instrumentation software standards maintained by the IVI Foundation.

### 1.2 Intended Audience and Scope

This specification is primarily intended for product developers interested in implementing and leveraging software features of the PXI platform. Hardware developers will be interested in using hardware description files for identifying and describing the capabilities of PXI hardware products such as chassis and system controller modules. Likewise, software developers and systems integrators should take advantage of hardware description files to manage PXI resources, including PXI triggers and the PXI local bus, and to implement features such as slot identification and chassis identification. Additionally, product developers and systems integrators should reference the operating system framework definitions to ensure system-level interoperability.

# 1.3 Background and Terminology

This section defines the acronyms and key words that are referred to throughout this specification. This specification uses the following acronyms:

- API—Application Programming Interface

- CompactPCI PICMG 2.0 Specification

- PCI—Peripheral Component Interconnect; electrical specification defined by PCISIG

- PCISIG—PCI Special Interest Group

- **PICMG**—PCI Industrial Computer Manufacturers Group

- PXI—PCI eXtensions for Instrumentation

- VISA—Virtual Instrument Software Architecture

- VPP—VXIplug&play Specification maintained by the IVI Foundation

This specification uses several key words, which are defined as follows:

**RULE:** Rules SHALL be followed to ensure compatibility. A rule is characterized by the use of the words SHALL and SHALL NOT.

**RECOMMENDATION:** Recommendations consist of advice to implementers that will affect the usability of the final module. A recommendation is characterized by the use of the words SHOULD and SHOULD NOT.

**PERMISSION:** Permissions clarify the areas of the specification that are not specifically prohibited. Permissions reassure the reader that a certain approach is acceptable and will cause no problems. A permission is characterized by the use of the word MAY.

**OBSERVATION:** Observations spell out implications of rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules, so that the reader understands why the rule must be followed.

**MAY:** A key word indicating flexibility of choice with no implied preference. This word is usually associated with a permission.

**SHALL:** A key word indicating a mandatory requirement. Designers SHALL implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification. This word is usually associated with a rule.

**SHOULD:** A key word indicating flexibility of choice with a strongly preferred implementation. This word is usually associated with a recommendation.

# 1.4 Applicable Documents

This specification defines extensions to the base PCI and CompactPCI specifications referenced in this section. It is assumed that the reader has a thorough understanding of PCI and CompactPCI. The CompactPCI specification refers to several other applicable documents with which the reader may want to become familiar. This specification refers to the following documents directly:

- PXI-1: PXI Hardware Specification

- VPP-4.3: The VISA Library Specification

- PXI-4: PXI Module Description File Specification

- PXI-6: PXI Express Software Specification

- PXI-9: PXI and PXI Express Trigger Management Specification

- PCI Local Bus Specification

- PICMG 2.0 R3.0 CompactPCI Specification

# 2. Hardware Description Files

This section defines the formats of the hardware description files and describes their use.

#### 2.1 Overview

The *PXI Hardware Specification* allows many variations of chassis and system controller modules. While many PCI hardware capabilities are self-describing (that is, their identities and capabilities can be determined using standard PCI hardware enumeration techniques), there is no standard hardware mechanism for identifying and managing many of the resources in a PXI system. The *PXI Software Specification* solves this problem by defining a set of hardware description files for PXI systems and the components that comprise them.

A primary goal of PXI's hardware description files is to enable application and device driver software to identify components based on their geographic characteristics (that is, chassis number and slot number) rather than their less user-friendly PCI logical address characteristics (PCI bus number, device number, and function number). For example, using a PXI system description file as a lookup table, an application or driver can map between a module's location on the PCI bus and its physical location in a PXI chassis. This functionality enables operators to quickly and easily distinguish between several similar modules using the chassis number and slot number.

Another goal of the hardware description files is to serve as a repository for managing PXI platform resources. PXI triggers, for example, are a shared hardware resource, and the trigger lines must be managed by a central reservation facility to guarantee the prevention of resource conflicts. Similarly, PXI's local bus lines are managed by software to guarantee that adjacent PXI modules do not use the local bus in a conflicting manner. In both of these cases, hardware description files serve as standard data storage for describing and managing these shared resources.

PXI hardware descriptions are contained in .ini files, which consist of ASCII text. The .ini file format is useful because it is both human readable and easily parsed by application and driver software.

The *PXI Software Specification* defines two hardware description file formats: system description files and chassis description files. The system description file is used to describe an overall PXI system and the components that comprise it. It is a collection of information obtained from several sources, including other hardware description files. The chassis description file is used to describe a PXI chassis and its features. Both of these file formats are described in detail below.

## 2.2 Common File Requirements

All hardware description files are .ini files. Each .ini file contains one or more sections, and each section contains one or more tag lines. Each tag line describes a specific property of the section.

In the context of PXI hardware description files, .ini file sections form *descriptors*. Descriptors describe PXI systems and the components that comprise them. Descriptors always correspond to unique .ini file sections.

RULE: Each . ini file SHALL contain only ASCII text and whitespace.

**RULE:** Horizontal whitespace SHALL be defined as any of the ASCII characters for horizontal tab and space.

**RULE:** Each .ini file SHALL contain only the following types of lines: comment lines, blank lines, section headers, or tag lines.

**RULE:** Each line SHALL end with a line ending, as described in *Software Frameworks and Requirements*.

**RULE:** A comment line SHALL begin with either the '#' character or the ';' character.

**RULE:** A section header line SHALL begin with the '[' character and end with the ']' character. Text between the two brackets SHALL identify the type of section.

**RULE:** ASCII double-quotes SHALL be the only valid characters used to quote values.

RULE: Scalar numeric values SHALL NOT be quoted.

RULE: List values, including lists of zero or one items, SHALL be quoted.

**RULE:** All scalar numeric values shall be radix-10 unless stated otherwise.

**RULE:** All values in the .ini files SHALL be considered case sensitive.

**RULE:** String values SHALL be quoted.

**RULE:** If at least one level of quotes are present surrounding a tag value, readers of the .ini file SHALL remove the outermost set of quotes before interpreting the value.

**OBSERVATION:** The above rule ensures backward compatibility with previous versions of this specification.

**PERMISSION:** Readers of .ini files MAY interpret a file in a case-insensitive manner to ensure compatibility with writers that predate this specification.

**RULE:** All readers of .ini files SHALL ignore sections with section headers that they do not recognize.

**RULE:** All readers of .ini files SHALL ignore lines that they do not recognize.

**RULE:** A tag line SHALL consist of the following three fields: tag, '=' character, and value.

**PERMISSION:** The three fields in a tagline MAY be separated by any amount of horizontal whitespace.

#### .ini File Format Example

```

# This line is a comment.

[Section1]

ExampleTag = 1

IsSpecialSectionTag = "No"

ExampleListTag = "1,2,3,4"

[Section2]

ExampleTag = 2

IsSpecialSectionTag = "Yes"

ExampleListTag = "5,6,7,8"

```

#### 2.2.1 Version Descriptor

PXI hardware description files include a version descriptor section. The version descriptor allows software to distinguish between .ini file formats as the *PXI Software Specification* evolves. For information on backward compatibility, refer to the *Backward Compatibility with Previous PXI Specifications* section below.

**RULE:** A hardware description file SHALL include a single version descriptor.

**RULE:** A version descriptor . ini section SHALL be named "Version".

Table 2-1.

Version Information Tag Line Descriptions

| Tag   | Valid Values                              | Description                                                                                                                                                                                                                |

|-------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Major | x, where x is a positive decimal integer. | This field indicates the major version number of a version <i>x.y</i> , where <i>x</i> is the major number and <i>y</i> is the minor number of the <i>PXI Software Specification</i> version that this file complies with. |

| Minor | y, where y is a positive decimal integer. | This field indicates the major version number of a version <i>x.y</i> , where <i>x</i> is the major number and <i>y</i> is the minor number of the <i>PXI Software Specification</i> version that this file complies with. |

#### **Version Descriptor Example**

[Version]

Major = 2

Minor = 5

**OBSERVATION:** A version descriptor is useful for identifying the *PXI Software Specification* file format that a hardware description file complies with.

#### 2.2.2 Backward Compatibility with Previous PXI Specifications

Backward compatibility is a key feature of the *PXI Software Specification*, and hardware descriptions files must be structured so that compatibility with previous PXI specification revisions can be achieved.

Beginning with the *PXI Software Specification*, Revision 2.1, the format of each type of hardware description file has been modified so that new features, such as multi-chassis PXI systems and multi-segmented PXI chassis, can be accurately described. To maintain backward compatibility, the following applies:

**PERMISSION:** In addition to the format defined in this specification, A PXI System Description file MAY include sections in the format of PXI Specifications prior to revision 2.1 of the *PXI Software Specification*.

Sections of the PXI System Description file that are in the format of specification revisions prior to version 2.1 are referred to as *legacy sections*.

**OBSERVATION:** None of the section headings in this specification overlap with headings defined in previous specifications. Multiple versions of the PXI System Description file format may exist together in the same System Description file.

**RULE:** Even if a PXI System Description file includes the legacy sections, it MUST include the sections defined in this specification.

**OBSERVATION**: For a System Description file to accurately describe a majority of PXI systems in use today, it must use the format defined in this specification. The legacy PXI System Description format cannot sufficiently describe modern PXI systems.

# 2.3 System Description Files

System description files describe PXI systems and their components. The system controller module and the one or more chassis that comprise a PXI system determine a system description. A system description enables a variety of software functionality, including geographic slot identification. Chassis description files, from which much of the system description content is derived, are discussed later in this chapter.

#### 2.3.1 System Description Definitions

To develop a system description, it is useful to define descriptors for the following PXI system components:

- **Resource Manager** A Resource Manager Descriptor provides information about the Resource Manager that created the system description file.

- System A PXI System descriptor corresponds to a physical PXI system. A PXI System is a collection of chassis. Multiple chassis in a system are coupled in a software-transparent manner (that is, they are coupled via PCI-PCI bridging).

- Chassis A chassis descriptor corresponds to a physical PXI chassis in a system. Chassis can include PCI bus segments, trigger buses, trigger bridges, star triggers, and slots. Line mapping specifications may be used to identify chassis capabilities to software.

- PCI Bus Segments A PCI bus segment descriptor corresponds to a distinct, physical PCI bus in a chassis. PCI bus segments can contain slots, bridges, and other backplane devices. Multiple PCI bus segments are linked within a chassis using PCI-PCI bridging.

- **Trigger Buses** A PXI trigger bus descriptor corresponds to a physical trigger bus in a chassis. A trigger bus is characterized by a list of slots sharing the physical trigger bus connection. Chassis can contain multiple trigger buses.

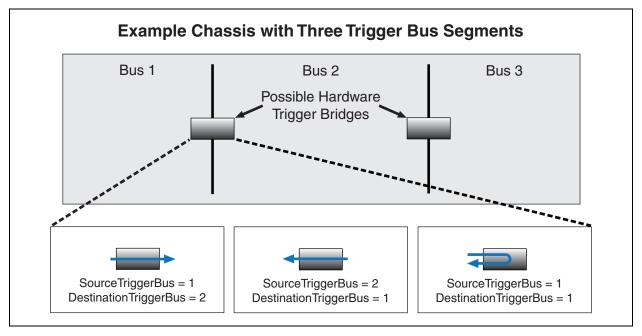

- **Trigger Bridges** A PXI trigger bridge descriptor corresponds to a physical trigger bridge in a PXI chassis. Each trigger bridge descriptor represents the possible unidirectional routes that can be established between two buses; if a physical trigger bridge can be used to establish routes in either direction between these buses, two trigger bridge descriptors must represent it, one for each direction. A chassis may contain multiple trigger bridges.

- Line Mapping Specifications A line mapping specification does not represent a physical chassis component, but sets out the possible routes that a trigger bridge can establish between two adjacent trigger buses. This line mapping provides software with detailed information about the routing capabilities that the chassis supports. These routes can be established through calls made to the chassis Trigger Manager, as described in PXI-9: PXI and PXI Express Trigger Management Specification. Multiple line mappings can describe a chassis' routing capabilities.

- Star Triggers A PXI star trigger descriptor corresponds to a physical set of star triggers in a chassis. A set of star triggers is characterized by a star trigger controller slot number and a mapping of PXI STAR lines (defined in the PXI Hardware Specification) to peripheral slot numbers. A chassis can contain multiple sets of star triggers.

- **Slots** –A PXI slot descriptor corresponds to a physical slot in a chassis. A slot is characterized by a geographic address, a PCI logical address, local bus routings, and other special capabilities. A chassis has multiple slots.

In addition, a Resource Manager is defined as the entity responsible for creating a PXI system description file. For example, the responsibilities of a Resource Manager might be accomplished by a systems integrator, or a software utility might be provided to automate the Resource Manager algorithm.

RULE: A system controller module manufacturer SHALL provide either a system description file for each supported system configuration or a Resource Manager utility that can manage the system description file.

**OBSERVATION:** A system controller module is any module that resides in slot 1 of a PXI chassis.

**RECOMMENDATION**: A system controller module manufacturer SHOULD provide a utility that can automate the Resource Manager algorithm.

**OBSERVATION:** *PXI-1: PXI Hardware Specification* does not define hardware mechanisms that provide for the automatic discovery of PXI chassis or PXI system controller modules. As a result, a software resource manager may require input from the user to facilitate discovery of these components.

**RULE**: A system description file SHALL be named pxisys.ini.

**RULE:** The pxisys.ini file SHALL be located as described in the *Software Frameworks* section of *PXI-6: PXI Express Software Specfication*.

**RECOMMENDATION**: To aid systems integrators and operators, PXI module configuration and driver software SHOULD use geographic addressing information, available in a PXI system description file, to present chassis and slot locations for PXI modules via a user interface.

#### 2.3.2 Resource Manager Descriptor

The Resource Manager descriptor provides information about how the system description file was generated. This information is intended for debugging purposes.

RULE: A system description file SHALL contain one and only one Resource Manager descriptor.

RULE: The Resource Manager descriptor . ini section header SHALL be named ResourceManager.

**RULE:** The Resource Manager descriptor section SHALL contain one of each tag line type described in Table 2-4.

| Tag       | Valid Values                                        | Description                                                                                                                                            |

|-----------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name      | The name of the Resource Manager.                   | This field identifies the Resource<br>Manager that last edited or created the<br>System Description File.                                              |

| Version   | A vendor-defined string.                            | This field should be populated with a vendor-defined string describing the version of the Resource Manager that generated the System Description File. |

| Timestamp | A string containing a human-readable date and time. | This field indicates the date and time when the file was last written by the Resource Manager.                                                         |

Table 2-2. Version Information Tag Line Descriptions

#### **Resource Manager Descriptor Example**

```

[ResourceManager]

Name = "PXISA Resource Manager"

Version = "1.0.0"

Timestamp = "August 29, 2011, 02:00:00 PM GMT-0400"

```

**RULE:** A software Resource Manager SHALL use its own name, as displayed in the Resource Manager's category key of the services tree, as the value for the Vendor tag.

**RECOMMENDATION:** If the system description file is generated by any means other than by a software Resource Manager, the name tag SHOULD describe the entity creating the file.

**RECOMMENDATION:** A software Resource Manager SHOULD populate the Version tag with a meaningful string that is unique to each version of the Resource Manager made available by the specified vendor.

**PERMISSION:** If the system description file is generated by any means other than by a software Resource Manager, any value, including an empty string, MAY be used for the Version tags.

**RULE:** The value of the Timestamp tag SHALL be a human readable date and time, with a resolution of at least 1 second.

**RECOMMENDATION:** The value of the Timestamp tag SHOULD include a time zone indication that is the same as the time zone of the system on which the system description file was created.

**OBSERVATION:** The Timestamp tag is intended to be used for debugging purposes only. For a date and time suitable for interpretation by software, the operating system provides a more relevant and accessible mechanism to retrieve the time when the system description file was last modified.

#### 2.3.3 System Descriptor

The system descriptor contains highest-level information about a PXI system. PXI systems are characterized by the chassis that comprise the system, and the system descriptor contains a list of these chassis.

**RULE:** A system description file SHALL contain one and only one system descriptor.

**RULE:** The system descriptor .ini section header SHALL be named "System".

**RULE:** Each system descriptor section SHALL contain one of each tag line types described in Table 2-3.

**Table 2-3.** System Description File – System Tag Line Descriptions

| Tag          | Valid Values                                                                         | Description                                      |

|--------------|--------------------------------------------------------------------------------------|--------------------------------------------------|

| Chassis List | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n \ge 1$ . | This tag enumerates the chassis in a PXI system. |

#### System Descriptor Example

```

# This section describes a PXI system with two chassis.

[System]

ChassisList = "1,2"

```

**RULE:** PXI chassis, specified with the ChassisList tag, SHALL be enumerated by a Resource Manager when collecting information regarding each chassis in the PXI system.

**OBSERVATION:** A Resource Manager can enumerate chassis using a variety of mechanisms. For example, a Resource Manager utility can present a user interface, allowing a user to identify the types of chassis included in the system.

**RULE:** Multiple chassis SHALL be uniquely numbered in the ChassisList tag.

**OBSERVATION:** Chassis can be numbered in an arbitrary fashion. For example, chassis can be numbered according to their order of discovery using a depth-first PCI traversal algorithm.

#### 2.3.4 Chassis Descriptor

A chassis descriptor provides a high-level description of an individual PXI chassis in a system. A chassis descriptor contains collections of the components that comprise a chassis, including PCI bus segments, trigger buses, sets of star triggers, and slots.

**RULE:** A system description file SHALL contain a distinct chassis descriptor for each physical chassis that comprises the PXI system.

**OBSERVATION:** Chassis are enumerated using a system descriptor's ChassisList tag.

**RULE:** A chassis descriptor SHALL be named "ChassisN", where N is the chassis number.

**RULE:** A Resource Manager SHALL derive chassis numbers from the ChassisList tag of a system descriptor (see Table 2-3).

**RECOMMENDATION:** The chassis number SHOULD be physically viewable on a chassis to assist operators in locating peripheral modules.

RULE: Each chassis descriptor SHALL contain one of each of the tag line types described in Table 2-4.

Table 2-4. System Description File – Chassis Tag Line Description

| Tag                 | Valid Values                                                                                                                                                                           | Description                                                                     |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| PCIBusSegmentList   | A comma-separated list of $n$ , where $n$ is a decimal integer such that $1 \le n \le 255$ .                                                                                           | This tag enumerates the PCI bus segments in a chassis.                          |

| TriggerBusList      | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n >= 1$ .                                                                                                    | This tag enumerates the trigger buses in a chassis.                             |

| StarTriggerList     | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n \ge 1$ .                                                                                                   | This tag enumerates the sets of star triggers in a chassis.                     |

| TriggerBridgeList   | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n \ge 1$ .                                                                                                   | This tag enumerates the trigger bridges in a chassis.                           |

| LineMappingSpecList | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n >= 1$ .                                                                                                    | This tag enumerates the line mapping specifications that exist for a chassis.   |

| SlotList            | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n >= 1$ .                                                                                                    | This tag enumerates the slots in a chassis.                                     |

| TriggerManager      | A string indicating the relative<br>path to the Trigger Manager to<br>use for the chassis, based at the<br>root of the Trigger Managers<br>portion of the Services Tree, or<br>"None." | This tag provides an indirect reference to the Trigger Manager for the chassis. |

| DescriptionFile     | A string containing a filename.                                                                                                                                                        | This tag identifies the filename of the chassis description file.               |

| Tag    | Valid Values                                          | Description                                |

|--------|-------------------------------------------------------|--------------------------------------------|

| Model  | A string indicating the model name for this chassis.  | This tag identifies a chassis model name.  |

| Vendor | A string indicating the vendor name for this chassis. | This tag identifies a chassis vendor name. |

**Table 2-4.** System Description File – Chassis Tag Line Description (Continued)

#### **Chassis Descriptor Example**

```

# This example describes a 3-segment, 18-slot PXI chassis

# with 2 bidirectional trigger bridges that have equivalent

# routing capabilities

[Chassis1]

PCIBusSegmentList = "1,2,3"

TriggerBusList = "1,2,3"

TriggerBridgeList = "1,2,3,4"

LineMappingSpecList = "1"

StarTriggerList = "1"

SlotList = "1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18"

TriggerManager = "PXISA\Example 18-Slot Chassis"

DescriptionFile = "PXISA Example 18-Slot Chassis.ini"

Model = "Example 18-Slot Chassis"

Vendor = "PXISA"

```

RULE: With the exceptions of the "TriggerManager" and "DescriptionFile" tags, a Resource Manager SHALL derive the tag values in Table 2-4 from the tag values of the corresponding chassis description file's chassis descriptor (see Table 2-11).

RULE: A Resource Manager SHALL set the "DescriptionFile" tag to the filename of the chassis description file for the chassis.

**OBSERVATION:** Software can use the "DescriptionFile" tag to easily locate the chassis description file for the chassis. This is useful if the vendor has included additional information in the chassis description file that has not been copied into the system description file, but which may be useful for vendor-specific behaviors.

**OBSERVATION:** The "DescriptionFile" tag does not include the full path to the chassis description file, because all chassis description files are in the same directory. Refer to section 2.4.

**RULE:** A Resource Manager SHALL set the TriggerBridgeList and LineMappingSpecList tag values to an empty list if the corresponding chassis description file's chassis descriptor does not contain these tags.

**RULE:** A Resource Manager SHALL set the value of the TriggerManager tag to *Vendor\Model*, where Vendor is the chassis vendor and Model is the chassis model, to indicate the specific Trigger Manager specified for the chassis model in the Services Tree, if such a specification is available there.

RULE: For chassis that do not have a specific trigger manager indicated in the Services Tree, a Resource Manager SHALL set the value of the TriggerManager tag to *Vendor*, where *Vendor* is the chassis vendor, to indicate the vendor default Trigger Manager for the vendor of the chassis, if such a vendor default trigger manager is specified.

RULE: For chassis that do not have a corresponding model-specific or vendor default Trigger Manager specified in the Services Tree, a Resource Manager SHALL set the value of the TriggerManager tag to *Vendor*, where *Vendor* is the default trigger manager's vendor.

**RULE:** A Resource Manager SHALL set the TriggerManager field to "None" if there is no chassis-appropriate trigger manager available, and the default Trigger Manager (refer to section 4.3.2) is set to "None."

**OBSERVATION:** If the TriggerManager field is "None," it signifies that no Trigger Manager is available for the chassis on the system, and any attempt to use a Trigger Manager for the chassis will fail.

**OBSERVATION:** This use case is expected to occur most commonly during the transition to the new specifications and become less common with time. The ability to use a default Trigger Manager from any vendor is intended to further limit the scope of this case.

**OBSERVATION:** The value for the TriggerManager tag is the relative path from the Trigger Managers category key to the key containing the trigger manager's specification, with elements separated by a backslash ("\").

**OBSERVATION:** The backslash ("\") will always be the delimiter for Services Tree keys in the system description file, regardless of whether the underlying operating system uses the backslash as a delimiter.

**OBSERVATION:** If the Services Tree does not specify a Trigger Manager for a chassis or for the vendor of that chassis, the software for the chassis predates *PXI-9: PXI and PXI Express Trigger Management Specification*. In this case, a default Trigger Manager is selected to handle reservations for the chassis, so that the chassis can work with software designed to call the Trigger Manager APIs. Refer to section 4.3.2 for more information about the default Trigger Manager.

#### 2.3.5 PCI Bus Segment Descriptor

A PCI bus segment descriptor describes an individual PCI bus segment in a chassis.

**RULE:** A system description file SHALL contain a distinct PCI bus segment descriptor for each physical PCI bus segment in the system.

**RULE:** A PCI bus segment descriptor SHALL be named "ChassisMPCIBusSegmentN", where M is the chassis number, and N is the PCI bus segment number.

**RULE:** A Resource Manager SHALL derive PCI bus segment numbers from the PCIBusSegmentList tag of the corresponding chassis descriptor (see Table 2-4).

**OBSERVATION:** While each PCI bus segment number will uniquely correspond to a PCI bus number, the PCI bus segment number will not necessarily be equal to the corresponding PCI bus number.

**RULE:** Each PCI bus segment descriptor SHALL contain one of each of tag line type described in Table 2-5.

| Tag      | Valid Values                                                                         | Description                                                  |

|----------|--------------------------------------------------------------------------------------|--------------------------------------------------------------|

| SlotList | A comma-separated list of $n$ , where $n$ is a decimal integer such that $n \ge 1$ . | This tag enumerates the physical slots on a PCI bus segment. |

**Table 2-5.** System Description File – PCI Bus Segment Tag Line Descriptions

#### **PCI Bus Segment Descriptor Example**

```

# This example describes the third bus segment of

# an 18-slot PXI chassis

[Chassis1PCIBusSegment3]

SlotList = "13,14,15,16,17,18"

```

RULE: A Resource Manager SHALL derive the tag values in Table 2-5 from the tag values of the corresponding chassis description file's PCI Bus Segment descriptor (see Table 2-12).

PERMISSION: A PCI bus segment descriptor that describes a segment with no PXI slots will contain an empty slot list. In this case, the PCI bus segment descriptor MAY be excluded from the system description file.

#### 2.3.6 Trigger Bus Descriptor

A trigger bus descriptor describes an individual trigger bus in a PXI chassis. A trigger bus is characterized by a list of slots that reside on the trigger bus.

**RULE:** A system description file SHALL contain a distinct PXI trigger bus descriptor for each physical PXI trigger bus in the system.

**RULE:** A trigger bus descriptor SHALL be named "Chassis MTriggerBus N", where M is the chassis number and *N* is the trigger bus number.

RULE: A Resource Manager SHALL derive trigger bus numbers from the TriggerBusList tag of the corresponding chassis descriptor (see Table 2-4).

**OBSERVATION:** While each trigger bus number will uniquely correspond to a set of PXI slots, there is not necessarily a one-to-one correspondence between trigger buses and PCI bus segments.

RULE: Each trigger bus descriptor SHALL contain one of each of the tag line types described in Table 2-6.

| Tag      | Valid Values                             | Description                                |

|----------|------------------------------------------|--------------------------------------------|

| SlotList | A comma-separated list of $n$ ,          | This tag enumerates the slots on a trigger |

|          | where <i>n</i> is a decimal integer such | bus.                                       |

|          | that $n >= 1$ .                          |                                            |

**Table 2-6.** System Description File - Trigger Bus Tag Line Descriptions

#### **Trigger Bus Descriptor Example**

```

# This example describes the first trigger bus of a

# 3-segment, 18-slot chassis.

[Chassis1TriggerBus1]

SlotList = "1,2,3,4,5,6"

```

RULE: A Resource Manager SHALL derive the tag values in Table 2-6 from the tag values of the corresponding chassis description file's Trigger Bus descriptor (see Table 2-13).

#### 2.3.7 Trigger Bridge Descriptor

A trigger bridge descriptor describes a unidirectional trigger bridge in a PXI chassis.

**RULE:** A trigger bridge descriptor SHALL be named *ChassisMTriggerBridgeN*, where *M* is the chassis number and N is the number of the trigger bridge.

RULE: A Resource Manager SHALL derive trigger bridge descriptor numbers from the TriggerBridgeList tag of the chassis descriptor (refer to Table 2-4).

**RULE:** Each trigger bridge descriptor SHALL contain one of each of the tagline types described in Table 2-7.

| Tag                   | Valid Values                                           | Description                                                                                         |

|-----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| SourceTriggerBus      | n, where $n$ is a decimal integer such that $n >= 1$ . | The source trigger bus for this trigger bridge.                                                     |

| DestinationTriggerBus | n, where $n$ is a decimal integer such that $n >= 1$ . | The destination trigger bus for this trigger bridge.                                                |

| LineMappingSpec       | n, where $n$ is a decimal integer such that $n >= 1$ . | The number of the line mapping spec that describes the routing capabilities of this trigger bridge. |

Table 2-7. System Description File – Trigger Bridge Descriptions

#### **Trigger Bridge Descriptor Example**

```

# This example describes a trigger bridge that

# can route signals from trigger bus 1 to trigger

# bus 2, with line-by-line capabilities described by

# LineMappingSpec 1.

[Chassis1TriggerBridge1]

SourceTriggerBus = 1

DestinationTriggerBus = 2

LineMappingSpec = 1

```

**RULE:** A Resource Manager SHALL derive the tag values in Table 2-7 from the tag values of the corresponding chassis description file's Trigger Bridge descriptor.

#### 2.3.8 Line Mapping Specification Descriptor

A line mapping specification describes the possible routes that can be established between a given source bus and destination bus. The line mapping specification is in a separate descriptor from the trigger bridge so that it can be referenced from multiple trigger bridge descriptors, avoiding unnecessary duplication of information about routing capabilities.

**OBSERVATION:** There is no direct relationship between the number of physical trigger bridges in a chassis and the number of line mapping specification descriptors necessary; there should be as many line mapping spec descriptors as there are unique sets of bus-to-bus routing capabilities provided by trigger routers. For example, if a chassis has three trigger bridges with equivalent routing capabilities in each direction, then only a single line mapping specification descriptor is necessary.

**RULE:** A line mapping specification descriptor SHALL be named *ChassisMLineMappingSpecN*, where *M* is the chassis number and *N* is the number for the line mapping specification.

**RULE:** A Resource Manager SHALL derive line mapping spec descriptor numbers from the LineMappingSpecList tag of the chassis descriptor (refer to Table 2-4).

**RULE:** Each line mapping spec descriptor SHALL contain one of each of the tagline types described in Table 2-8.

| Tag                                                                                                                                                                                                          | Valid Values                                                                               | Description                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| PXI_TRIGn, where n is an integer that represents a PXI trigger line on the source trigger bus of the trigger bridge referencing this descriptor. One tag must exist for each trigger line on the source bus. | A comma-separated list of $n$ , where $n$ is a decimal integer such that $0 \le n \le 7$ . | This tag enumerates the lines on the destination trigger bus to which the signal on the source line can be routed. |

#### **Line Mapping Spec Descriptor Example**

```

# This example describes a line mapping in which

# the referencing trigger bridge can map any line on the

# source trigger bus to any line on the destination

# trigger bus.

[Chassis1LineMappingSpec1]

PXI_TRIG0 = "0,1,2,3,4,5,6,7"

PXI_TRIG1 = "0,1,2,3,4,5,6,7"

PXI_TRIG2 = "0,1,2,3,4,5,6,7"

PXI_TRIG3 = "0,1,2,3,4,5,6,7"

PXI_TRIG4 = "0,1,2,3,4,5,6,7"

PXI_TRIG5 = "0,1,2,3,4,5,6,7"

PXI_TRIG6 = "0,1,2,3,4,5,6,7"

PXI_TRIG6 = "0,1,2,3,4,5,6,7"

```

**RULE:** A Resource Manager SHALL derive the tag values in Table 2-8 from the tag values of the corresponding chassis description file's Line Mapping Spec descriptor (refer to Table 2-8).

#### 2.3.9 Star Trigger Descriptor

A star trigger descriptor describes an individual set of star triggers in a PXI chassis. A star trigger descriptor is characterized by a star trigger controller slot number and a mapping of PXI\_STAR lines, as defined in the *PXI Hardware Specification*, to peripheral slot numbers.

**RULE:** A system description file SHALL contain a distinct PXI star trigger descriptor for each physical set of PXI star triggers in the system.

**RULE:** A trigger bus descriptor SHALL be named "Chassis MStar Trigger N", where M is the chassis number and N is the number for the set of star triggers.

**RULE:** A Resource Manager SHALL derive star trigger descriptor numbers from the StarTriggerList tag of the corresponding chassis descriptor (see Table 2-4).

RULE: Each star trigger descriptor SHALL contain one of each of the tag line types described in Table 2-9.

| Tag                                                                                                                                         | Valid Values                                                                                    | Description                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| ControllerSlot                                                                                                                              | A decimal integer $n$ , where $n$ is a decimal integer such that $n \ge 1$ .                    | This tag specifies the star trigger controller slot number for a PXI_STAR lines in a set of star triggers. |

| PXI_STAR $n$ (where $n$ is a decimal integer such that $0 \le n$ $\le 12$ ), for each PXI star trigger line physically routed to a PXI slot | A decimal integer m, where m is a valid PXI slot number that connects to the star trigger line. | This tag specifies the PXI_STAR line to slot mapping for a set of star triggers.                           |

Table 2-9. System Description File – Star Trigger Tag Line Descriptions

#### **Star Trigger Descriptor Example**

```

# This example describes a set of star triggers for a

# 3-segment, 18-slot chassis.

[Chassis1StarTrigger1]

ControllerSlot = 2

PXI STAR0 = 3

PXI_STAR1 = 4

PXI\_STAR2 = 5

PXI\_STAR3 = 6

PXI\_STAR4 = 7

PXI\_STAR5 = 8

PXI_STAR6 = 9

PXI\_STAR7 = 10

PXI_STAR8 = 11

PXI\_STAR9 = 12

PXI\_STAR10 = 13

PXI STAR11 = 14

PXI_STAR12 = 15

```

**RULE:** A Resource Manager SHALL derive the tag values in Table 2-9 from the tag values of the corresponding chassis description file's Star Trigger descriptor (see Table 2-16).

**OBSERVATION:** The star trigger descriptor allows configuration software to describe alternative star trigger line mappings.

**OBSERVATION:** If a star trigger line is not routed to a PXI slot, the corresponding PXI\_STAR*n* tag will not be listed in the star trigger bus descriptor.

#### 2.3.10 Slot Descriptor

A slot descriptor describes an individual slot in a chassis. A slot descriptor is characterized by the features of the slot it describes, including routing information for the slot's local bus lines and the PCI logical address for a module that might occupy the slot. The slot descriptor serves as a lookup facility for applications and driver software interested in geographic slot identification.

**RULE:** A system description file SHALL contain a distinct slot descriptor for each physical slot in the PXI system.

**RULE:** A slot descriptor SHALL be named "ChassisMSlotN", where M is the chassis number, and N is the physical slot number.

RULE: A Resource Manager SHALL derive slot numbers from the SlotList tag of the corresponding chassis descriptor (see Table 2-4).

RULE: Each slot descriptor SHALL contain one of each of non-shaded tag line type described in Table 2-10, except where stated otherwise in this section.

PERMISSION: Application and device driver software MAY continue to use the shaded fields of Table 2-10. These fields may be removed in a future revision.

**RECOMMENDATION:** New software development SHOULD use the non-shaded fields.

Table 2-10. System Description File – Slot Tag Line Descriptions

| Tag                        | Valid Values                                                                                                                                | Description                                                                                         |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| PCISlotPath                | A string containing a comma-separated list of <i>n</i> , where <i>n</i> is a hexadecimal integer indicating the slot path of this PXI slot. | This tag indicates the PCI slot path for a slot.                                                    |

| PCISlotPathRootBus         | $n$ , where $n$ is a decimal integer such that $0 \le n \le 255$ .                                                                          | This tag indicates the bus number of the PCI root at which the PCISlotPath is based.                |

| LocalBusLeft               | A valid slot descriptor.  A valid star trigger descriptor.  (Other).                                                                        | This tag indicates how a slot routes its local bus pins to the left.                                |

| LocalBusRight              | A valid slot descriptor. (Other).                                                                                                           | This tag indicates how a slot routes its local bus pins to the right.                               |

| PCIBusNumber               | $n$ , where $n$ is a decimal integer such that $0 \le n \le 255$ .                                                                          | This tag indicates the PCI bus number for a slot.                                                   |

| PCIDeviceNumber            | $n$ , where $n$ is a decimal integer such that $0 \le n \le 31$ .                                                                           | This tag indicates the PCI device number for a slot.                                                |

| ExternalBackplaneInterface | None.<br>(Other).                                                                                                                           | If a slot routes to an external backplane interface, this tag specifies the name of that interface. |

#### **Slot Descriptor Example**

```

# This example describes Slot 2 of an 8-slot PXI chassis.

[Chassis1Slot2]

# To calculate the slot path, we note that this chassis sits

# behind a PCI-PCI bridge residing on PCI bus 0 at PCI

# device 17

PCISlotPath = "98,88"

PCISlotPathRootBus = 0

PCIBusNumber = 2

PCIDeviceNumber = 19

LocalBusLeft = "StarTrigger1"

LocalBusRight = "Chassis1Slot3"

```

**RULE:** A Resource Manager SHALL derive the LocalBusLeft, LocalBusRight, and ExternalBackplaneInterface tag values from the tag values in the corresponding chassis description file's slot descriptor (see Table 2-18).

**RULE:** For all slots except Slot 1, a PXI Resource Manager SHALL derive the PCISlotPath, PCISlotPathRootBus, PCIBusNumber, and PCIDeviceNumber tag values from the controller IDSEL routing information, the PCI bus segment IDSEL routing information (see Table 2-12), and the PCI bus hierarchy.

**RULE:** For Slot 1, a PXI Resource Manager SHALL set the PCISlotPath and PCISlotPathRootBus to reflect the location of the PCI Bridge, root port, or switch port on the system controller which connects to the chassis backplane.

**OBSERVATION:** Satisfying the above RULE requires no additional knowledge of the system controller. The necessary information can be determined by starting with the PCISlotPath for any other slot, and walking the PCI bus hierarchy back to the system controller using the information in the chassis description file.

**RULE:** If the chassis backplane is connected directly to the PCI root bus, the value of PCISlotPath SHALL be set to an empty string (""), and PCISlotPathRootBus SHALL be set the bus number of the root bus.

**OBSERVATION:** Taken together, the PCISlotPath and PCISlotPathRootBus for slot 1 provide a reliable identifier for a given chassis that will persist across system reboots, assuming the hardware configuration is not changed.

**RULE:** For Slot 1, a PXI Resource Manager SHALL NOT populate the PCIBusNumber and PCIDeviceNumber tag values.

**OBSERVATION:** A PXI slot that does not implement the full set of PXI features, such as a CompactPCI-only slot, will have tag values corresponding to PXI features set to "None". For example, a CompactPCI-only slot descriptor would have LocalBusLeft and LocalBusRight tags set to "None". In addition, this slot would not be present in the SlotList for a trigger bus, and it would not belong to a set of star triggers.

#### 2.3.10.1 PCI Slot Path

To facilitate geographic slot identification, it is useful to introduce the concept of a PCI slot path. The purpose of a PCI slot path is to describe the PCI bus hierarchy in a manner independent of the PCI bus number. PCI slot paths are a sequence of hexadecimal values representing the PCI device number and function number of a PCI module and each parent PCI bridge that routes the module to the host PCI bridge (bus 0). Each byte of a slot path corresponds to the PCI BIOS device/function number encoding for the current bridge in the path. The encoding is calculated as follows:

PCI Slot Path Byte = (PCI Device Number << 3) | PCI Function Number

#### **PCI Slot Path Example**

Consider a PXI slot located on PCI bus #2, device #17d. This slot is subordinate to a PCI-PCI bridge with primary bus #0, device #14d. The slot path for this device would be "88,70", that is, ((17d << 3) | 0) followed by ((14d << 3) | 0).

**OBSERVATION:** Slot paths are useful because they change less frequently than PCI bus numbers. In PXI systems, if a PCI bus number changes, the PCI slot path for slots on that segment do not necessarily change.

**OBSERVATION:** A slot path describes the hierarchical location of a device relative to a PCI root. Because some systems have more than one PCI root, this specification requires that wherever a slot path is indicated in a description file, it is accompanied by the bus number of the root to which it applies.

**RECOMMENDATION:** Slot paths, along with their relevant root bus, SHOULD be used for mapping between PCI logical addresses to PXI geographic addresses.

**RULE:** Slot paths SHALL be represented as strings in .ini files.

#### 2.3.10.2 Local Bus Routings

The slot descriptor provides a means for specifying how the local bus lines are routed for a given slot.

**OBSERVATION:** The LocalBusLeft and LocalBusRight tags will usually specify the slot descriptor for the slot to the left and right of the current slot, respectively.

**OBSERVATION:** If a slot does not route its local bus pins (left or right) to a neighboring slot's local bus, the LocalBus tags can be used to specify a special slot capability.

**OBSERVATION:** The LocalBusLeft tag for PXI slot 2 can be used to specify the Star Trigger capability, pointing to a chassis' StarTrigger descriptor.

**OBSERVATION:** The LocalBusRight tag to the rightmost slot in a chassis can be used to specify a connection to an external backplane interface.

**RECOMMENDATION:** The LocalBusLeft and LocalBusRight tags SHOULD be used to specify an external backplane connection. The ExternalBackplaneInterface tag is provided for backward compatibility only.

#### 2.3.11 System Description File Example

```

# This example describes a PXI system with two chassis.

# The first chassis (Chassis1) has a single PXI bus

# segment and 8 PXI slots, described by the chassis

# description file in Example 2.4.10.1.

# The second chassis (Chassis2) has 3 PXI bus

# segments and 18 PXI slots, described by the chassis

# description file in Example 2.4.10.2.

# Assumptions:

# The two chassis (Chassis1 and Chassis2) are linked

# together using PXI-PXI bridging. The first chassis

# in the daisy-chain (Chassis1) contains a system

# controller module with a PCI-PCI bridge at PCI bus #0,

# device #30, function #0. Its corresponding PCI slot

# path node is 0xF0. This bridge forms the PXI bus

# segment (PCI bus #1) for Chassis1. The PXI-PXI bridge

# resides in slot #5 (PCI bus #1, device #12, function #0)

# of Chassis1. This split-bridge forms the first PXI

# segment of Chassis2 (PCI bus #3). Its corresponding

# PCI slot path node is 0x60. Chassis2 contains three

# PXI bus segments. The first segment contains a PCI-PCI

# bridge at PCI bus #3 device #12, function #0. Its

# corresponding PCI slot path node is 0x60. This

# bridge forms the second PXI bus segment (PCI bus #4).

# The second segment contains a PCI-PCI bridge at

# PCI bus #4, device #12, function #0. Its corresponding

# PCI slot path node is 0x60. This bridge forms the third

# PXI bus segment. The first chassis has no trigger routing

```

```

# capabilities. The second chassis has a

# trigger bridge between each segment. Any trigger

# line in the first segment can be routed to any line

# in the second segment, and vice-versa. Also, any line in

# the second segment can be routed to the same line in

# the third segment.

[Version]

Major = 2

Minor = 4

[PXI System]

ChassisList = "1,2"

[Chassis1]

Model = "Example 8-Slot Chassis"

Vendor = "PXISA"

PCIBusSegmentList = "1"

SlotList = "1,2,3,4,5,6,7,8"

TriggerBusList = "1"

TriggerManager = "PXISA"

StarTriggerList = "1"

[Chassis1StarTrigger1]

ControllerSlot = 2

PXI\_STAR0 = 3

PXI\_STAR1 = 4

PXI\_STAR2 = 5

PXI\_STAR3 = 6

PXI\_STAR4 = 7

PXI_STAR5 = 8

[Chassis1PCIBusSegment1]

SlotList = "1,2,3,4,5,6,7,8"

[Chassis1TriggerBus1]

SlotList = "1,2,3,4,5,6,7,8"

[Chassis1Slot1]

PCISlotPath = "F0"

PCISlotPathRootBus = 0

PCIBusNumber = "None"

PCIDeviceNumber = "None"

LocalBusLeft = "None"

LocalBusRight = "None"

ExternalBackplaneInterface = "None"

[Chassis1Slot2]

PCISlotPath = "78,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 15

LocalBusLeft = "StarTrigger1"

LocalBusRight = "Slot3"

```

```

ExternalBackplaneInterface = "None"

[Chassis1Slot3]

PCISlotPath = "70,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 14

LocalBusLeft = "Slot2"

LocalBusRight = "Slot4"

ExternalBackplaneInterface = "None"

[Chassis1Slot4]

PCISlotPath = "68,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 13

LocalBusLeft = "Slot3"

LocalBusRight = "Slot5"

ExternalBackplaneInterface = "None"

[Chassis1Slot5]

PCISlotPath = "60,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 12

LocalBusLeft = "Slot4"

LocalBusRight = "Slot6"

ExternalBackplaneInterface = "None"

[Chassis1Slot6]

PCISlotPath = "58,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 11

LocalBusLeft = "Slot5"

LocalBusRight = "Slot7"

ExternalBackplaneInterface = "None"

[Chassis1Slot7]

PCISlotPath = "50,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 10

LocalBusLeft = "Slot6"

LocalBusRight = "Slot8"

ExternalBackplaneInterface = "None"

[Chassis1Slot8]

PCISlotPath = "48,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 1

PCIDeviceNumber = 9

LocalBusLeft = "Slot7"

LocalBusRight = "None"

```

```

ExternalBackplaneInterface = "None"

[Chassis2]

Model = "Example 18-Slot Chassis"

Vendor = "PXISA"

PCIBusSegmentList = "1,2,3"

SlotList = "1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18"

TriggerBusList = "1,2,3"

TriggerBridgeList = "1,2,3"

LineMappingSpecList = "1,2"

TriggerManager = "PXISA\Example 18-Slot Chassis"

StarTriggerList = "1"

[Chassis2TriggerBridge1]

SourceTriggerBus = 1

DestinationTriggerBus = 2

LineMappingSpec = 1

[Chassis2TriggerBridge2]

SourceTriggerBus = 2

DestinationTriggerBus = 1

LineMappingSpec = 1

[Chassis2TriggerBridge3]

SourceTriggerBus = 2

DestinationTriggerBus = 3

LineMappingSpec = 2

[Chassis2LineMappingSpec1]

PXI\_TRIG0 = "0,1,2,3,4,5,6,7"

PXI\_TRIG1 = "0,1,2,3,4,5,6,7"

PXI\_TRIG2 = "0,1,2,3,4,5,6,7"

PXI\_TRIG3 = "0,1,2,3,4,5,6,7"

PXI\_TRIG4 = "0,1,2,3,4,5,6,7"

PXI\_TRIG5 = "0,1,2,3,4,5,6,7"

PXI\_TRIG6 = "0,1,2,3,4,5,6,7"

PXI\_TRIG7 = "0,1,2,3,4,5,6,7"

[Chassis2LineMappingSpec2]

PXI_TRIG0 = "0"

PXI_TRIG1 = "1"

PXI\_TRIG2 = "2"

PXI_TRIG3 = "3"

PXI\_TRIG4 = "4"

PXI_TRIG5 = "5"

PXI\_TRIG6 = "6"

PXI_TRIG7 = "7"

[Chassis2StarTrigger1]

ControllerSlot = 2

PXI\_STAR0 = 3

PXI_STAR1 = 4

PXI\_STAR2 = 5

PXI\_STAR3 = 6

```

```

PXI\_STAR4 = 7

PXI\_STAR5 = 8

PXI_STAR6 = 9

PXI\_STAR7 = 10

PXI\_STAR8 = 11

PXI\_STAR9 = 12

PXI\_STAR10 = 13

PXI\_STAR11 = 14

PXI\_STAR12 = 15

[Chassis2PCIBusSegment1]

SlotList = "1,2,3,4,5,6"

[Chassis2TriggerBus1]

SlotList = "1,2,3,4,5,6"

[Chassis2Slot1]

PCISlotPath = "None"

PCISlotPathRootBus = "None"

PCIBusNumber = "None"

PCIDeviceNumber = "None"

LocalBusLeft = "None"

LocalBusRight = "None"

ExternalBackplaneInterface = "None"

[Chassis2Slot2]

PCISlotPath = "78,60,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 3

PCIDeviceNumber = 15

LocalBusLeft = "StarTrigger1"

LocalBusRight = "Slot3"

ExternalBackplaneInterface = "None"

[Chassis2Slot3]

PCISlotPath = "70,60,F0"

PCISlotPathRootBus = 0

PCIBusNumber = 3

PCIDeviceNumber = 14

LocalBusLeft = "Slot2"

LocalBusRight = "Slot4"

ExternalBackplaneInterface = "None"